# TOWARDS A DEPENDABLE HOMOGENEOUS MANY-PROCESSOR SYSTEM-ON-CHIP

Xiao Zhang

#### Members of the dissertation committee:

Prof.dr.ir. G.J.M. Smit University of Twente (promotor)

Dr.ir. H.G. Kerkhoff University of Twente (co-promotor)

Prof.dr. P.M.G. Apers University of Twente (chairman and secretary)

Prof.dr.ir. J.P. Katoen University of Twente Prof.dr. J.L. Hurink University of Twente

Prof.dr.ir. J.Pineda de Gyves Eindhoven University of Technology

Prof.dr. Z. Peng Linköping University Dr.ir. H.G.H Vermeulen NXP Semiconductors

This research is conducted within the FP7 Cuttingedge Reconfigurable ICs for Stream Processing (CRISP) project (ICT-215881) supported by the European Commission.

Centre for Telematics and Information Technology P.O.Box 217 7500AE Enschede The Netherlands

Copyright © 2014 by Xiao Zhang, Enschede, the Netherlands.

All rights reserved. No part of this book may be reproduced or transmitted, in any form or by any means, electronic or mechanical, including photocopying, microfilming, and recording, or by any information storage or retrieval system, without the prior written permission of the author.

The cover page was designed by KTidea (www.ktidea.com), China. The thesis was printed by Gildeprint, the Netherlands.

ISBN 978-90-365-3772-8

DOI 10.3990/1.9789036537728

# TOWARDS A DEPENDABLE HOMOGENEOUS MANY-PROCESSOR SYSTEM-ON-CHIP

### **DISSERTATION**

to obtain

the degree of doctor at the University of Twente

on the authority of the rector magnificus,

prof. dr. H. Brinksma,

on account of the decision of the graduation committee,

to be publicly defended

on Thursday 30th of October 2014 at 16:45

by

Xiao Zhang

born on 17th June 1981 in Yantai, China

# This dissertation is approved by

Prof.dr.ir. G.J.M. Smit University of Twente (promotor)

Dr.ir. H.G. Kerkhoff University of Twente (co-promotor)

#### Abstract

Nowadays, dependable computing systems are widely required in mission-critical and human-life critical applications. While the advance in CMOS technology enables smaller and faster circuits, the dependability of modern ICs has worsened as a result of the shrinking dimensions of MOS transistors and the increasing complexity of semiconductor devices. For those very complex SoC with many processor cores, dependability enhancement approaches are especially important.

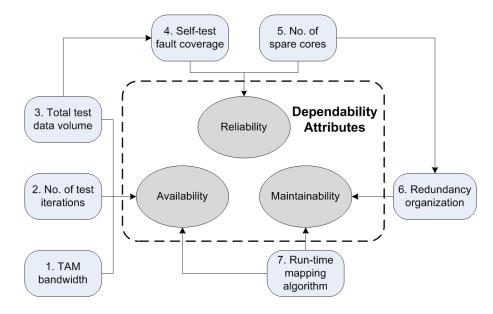

In this thesis we first examine the important attributes of a dependable MP-SoC. We then explore the possible approaches to enhance these attributes. The cost of the chosen dependability approach in terms of performance and resource (silicon area/energy) overhead are evaluated. The proposed dependability approach is implemented in silicon and its effectiveness is assessed using experiments and actual measurement results.

In the scope of this thesis, the dependability of an MPSoC is defined as its ability to deliver expected services under given conditions. Three important dependability attributes being reliability, availability and maintainability are identified. Reliability denotes the probability that the MPSoC will fail after a certain period of time. For an MPSoC, maintainability refers to the isolation/bypass of faulty components and reconfiguration of the fault-free spare parts to maintain its functionality. Availability denotes the readiness of the MPSoC to provide correct service.

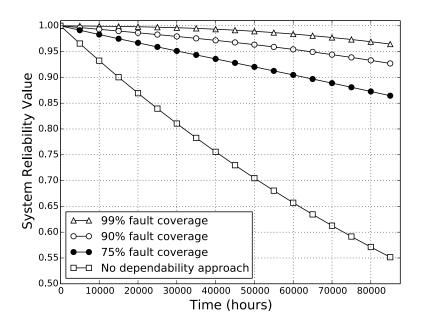

The reliability of an MPSoC can be improved by using processor cores as spare. Theoretically, system reliability greatly increases as more cores are used as spares. At the same time, the area overhead for reliability enhancement also increases. Maintainability can be realized by incorporating fault detection and self-repair features into an MPSoC. By dynamically detecting faults and reconfiguring the system to circumvent them, the system can be regarded as functionally correct

with a possible drop in performance. The time spent for fault detection and system repair is combined as system down time. Faster fault detection and repair operations will decrease system down time and enable a highly available MPSoC.

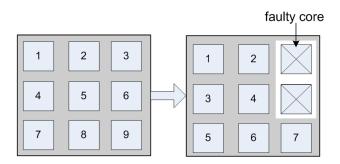

The dependability approach proposed in this thesis involves test aiming stuckat faults performed at the processor core level at application run-time. Once detected, faulty resources can be isolated by the so-called resource management software and core-level system repair can be performed by means of resource reconfiguration.

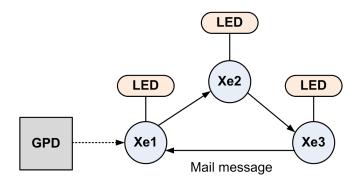

In order to validate the feasibility of our dependability approach, a homogeneous MPSoC platform with multiple Xentium processing cores was adopted as the vehicle of our experiment. A stand-alone infrastructural IP block, namely the Dependability Manager (DM), has been designed and integrated into the MPSoC platform. The DM can generate the test vectors for the Xentium cores, broadcast them via a Network-on-Chip and then collect the test responses from the cores under test. Since the cores under test have identical architecture, a faulty core can be detected by majority-voting the test responses. Dedicated test wrappers and NoC (reused as a TAM) were included into the platform MPSoC as well. A modified scan-based test scheme was used for a back-pressure style test data flow control by pausing and resuming the test data in the NoC.

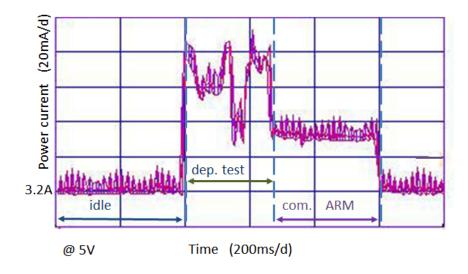

The MPSoC platform was fabricated as a Reconfigurable Fabric Device using UMC 90nm CMOS technology. The dependability overhead in terms of silicon area is about 1%. Experimental results show that the dependability test can be carried out at application run-time without interrupting the function of other applications. The inclusion of the DM into the RFD makes it a maintainable MPSoC with very short stuck-at and memory fault detection time (21ms) and reasonable MDT (hundreds of milliseconds).

In conclusion, our proposed dependability approach and dependability test methods have proven to be feasible and efficient. The successful integration of the DM into the RFD and its correct operation indicate that our dependability approach can be applied to other homogeneous MPSoC platforms for dependability improvement.

## Acknowledgements

This thesis would not have been accomplished without the help of many people. I would like to express my sincere gratitude for their kind support in a memorable period of my life.

First and foremost, my gratitude goes to my supervisor Dr. Hans Kerkhoff. I first met Hans when I was looking for an individual project as a Master student of the University of Twente. Then I did my Master thesis project (BioDrop) and my Ph.D research work with him all along. Not only because his research projects attracted me, but his patience, motivation, enthusiasm, and immense knowledge gave me a great deal of courage to explore in the scientific world. His guidance helped me in all the time of research and accomplishing this thesis. I can not imagine having a better advisor and mentor for my oversea study.

I would like to thank my promoter, Professor Gerard Smit, for his guidance in the CRISP project and his help with my thesis. I also highly appreciate the direct and indirect help of my colleagues such as Xiaoqin Sheng, Jinbo Wan, Yong Zhao, Mark Westmijze, Timon ter Braak, Hermen Toersche, Alireza Rohani, Muhammad Aamir Khan, etc. with my research work in the CAES group.

Since I arrived in the Netherlands in year 2004, I have spent eight years studying in the University of Twente and living in the city of Enschede. My life was made enjoyable by my Chinese and Dutch friends here. I would like to thank them all for showing up in my life and enjoying it with me.

Last but not least, I would like to thank my parents who have loved and supported me in every possible way for so many years.

# Contents

| Li       | st of | Acror                   | nyms                                                  | V  |

|----------|-------|-------------------------|-------------------------------------------------------|----|

| 1        | Inti  | $\operatorname{roduct}$ | ion                                                   | 1  |

|          | 1.1   | Resea                   | rch problem statement                                 | 2  |

|          | 1.2   | The C                   | CRISP project                                         | 4  |

|          | 1.3   | Contr                   | ibution of this thesis                                | 5  |

|          | 1.4   | Outlin                  | ne of this thesis                                     | 6  |

| <b>2</b> | Tre   | nds in                  | CMOS Technology, System Design and Dependability      |    |

|          | Cha   | allenge                 | es                                                    | 9  |

|          | 2.1   | Deper                   | ndability challenges                                  | 9  |

|          |       | 2.1.1                   | CMOS scaling and complexity                           | 9  |

|          |       | 2.1.2                   | Application reliability and availability requirements | 11 |

|          | 2.2   | Produ                   | action and life cycle of semiconductor devices        | 12 |

|          |       | 2.2.1                   | A brief introduction to semiconductor manufacturing   | 12 |

|          |       | 2.2.2                   | Taxonomy and terminology                              | 13 |

|          |       | 2.2.3                   | IC life cycle and failure rate                        | 14 |

|          | 2.3   | Faults                  | s occurring during IC lifetime                        | 17 |

|          |       | 2.3.1                   | Negative/positive bias temperature instability        | 17 |

|          |       | 2.3.2                   | Hot carrier injection (HCI)                           | 18 |

|          |       | 2.3.3                   | Time-dependent dielectric breakdown (TDDB)            | 18 |

|          |       | 2.3.4                   | Electromigration (EM)                                 | 19 |

|          |       | 2.3.5                   | Fault models                                          | 19 |

|          | 2.4   | Basics                  | s of testing                                          | 20 |

|          | 2.5   |                         | usion                                                 | 22 |

### CONTENTS

| 3 | The | Depe   | ndable MPSoC Concept                                    | <b>25</b> |

|---|-----|--------|---------------------------------------------------------|-----------|

|   | 3.1 | Introd | luction into dependable computing systems               | 26        |

|   | 3.2 | MPSo   | C reliability                                           | 28        |

|   |     | 3.2.1  | The reliability function                                | 28        |

|   |     | 3.2.2  | Realistic MPSoC reliability and our assumption          | 30        |

|   |     | 3.2.3  | Series and parallel system reliability                  | 30        |

|   |     | 3.2.4  | K-out-of-N:G system reliability                         | 32        |

|   |     | 3.2.5  | Improving MPSoC reliability                             | 35        |

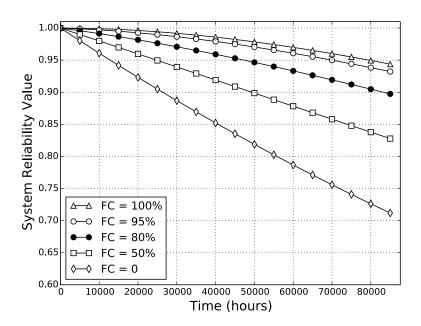

|   |     | 3.2.6  | Fault coverage and reliability                          | 39        |

|   | 3.3 | MPSo   | C availability and maintainability                      | 41        |

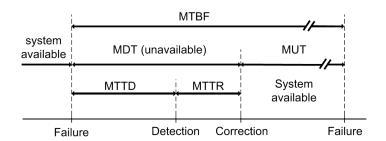

|   |     | 3.3.1  | Introduction to availability and maintainability        | 42        |

|   |     | 3.3.2  | A maintainable MPSoC                                    | 43        |

|   |     | 3.3.3  | Improvement of MPSoC availability                       | 47        |

|   | 3.4 | Design | n for Dependability                                     | 49        |

|   | 3.5 | Concl  | usion                                                   | 51        |

| 4 | The | Depe   | ndability Approach                                      | 53        |

|   | 4.1 | The d  | ependability approach                                   | 54        |

|   |     | 4.1.1  | MPSoC self-test                                         | 54        |

|   |     | 4.1.2  | MPSoC self-repair                                       | 56        |

|   | 4.2 | Deper  | idability test concept and architecture                 | 57        |

|   |     | 4.2.1  | Previous research on MPSoC testing                      | 57        |

|   |     | 4.2.2  | Dependability test architecture for a NoC-based homoge- |           |

|   |     |        | neous MPSoC                                             | 59        |

|   |     | 4.2.3  | Dependability test requirements and trade-offs          | 63        |

|   | 4.3 | Depen  | adability test infrastructure                           | 65        |

|   |     | 4.3.1  | Background of the NoC                                   | 65        |

|   |     | 4.3.2  | Reuse a GuarVC NoC as a TAM                             | 67        |

|   |     | 4.3.3  | Core test-wrapper                                       | 70        |

|   | 4.4 | Depen  | adability test at application run-time                  | 78        |

|   |     | 4.4.1  | Dependability test scheduling                           | 78        |

|   |     | 4.4.2  | The modified scan-based test                            | 80        |

|   |     | 4.4.3  | Impact of the dependability test                        | 83        |

### CONTENTS

|   | 4.5 | Testing | g the NoC                                                | 85  |

|---|-----|---------|----------------------------------------------------------|-----|

|   |     | 4.5.1   | NoC fault modeling                                       | 86  |

|   |     | 4.5.2   | NoC test and diagnosis concept                           | 87  |

|   | 4.6 | Conclu  | asions                                                   | 89  |

| 5 | Dep | endab   | ility Manager Architecture                               | 91  |

|   | 5.1 | Introd  | uction                                                   | 91  |

|   |     | 5.1.1   | DM overview                                              | 91  |

|   |     | 5.1.2   | The Xentium tile from a test perspective                 | 95  |

|   | 5.2 | Test-pa | attern compression theory                                | 97  |

|   | 5.3 | Reseed  | ling TPG architecture                                    | 101 |

|   |     | 5.3.1   | LFSR                                                     | 101 |

|   |     | 5.3.2   | Seed Calculation                                         | 103 |

|   |     | 5.3.3   | Prior studies of the reseeding technique                 | 105 |

|   |     | 5.3.4   | Logic triggered reseeding                                | 107 |

|   |     | 5.3.5   | Two-Dimensional Test-Vector Generation and Phase Shifter | 110 |

|   | 5.4 | Design  | and Implementation of the DM-TPG                         | 113 |

|   |     | 5.4.1   | Design of the reseeding TPG                              | 113 |

|   |     | 5.4.2   | DM-TPG implementation and simulation results             | 119 |

|   |     | 5.4.3   | Efficiency of the reseeding method                       | 121 |

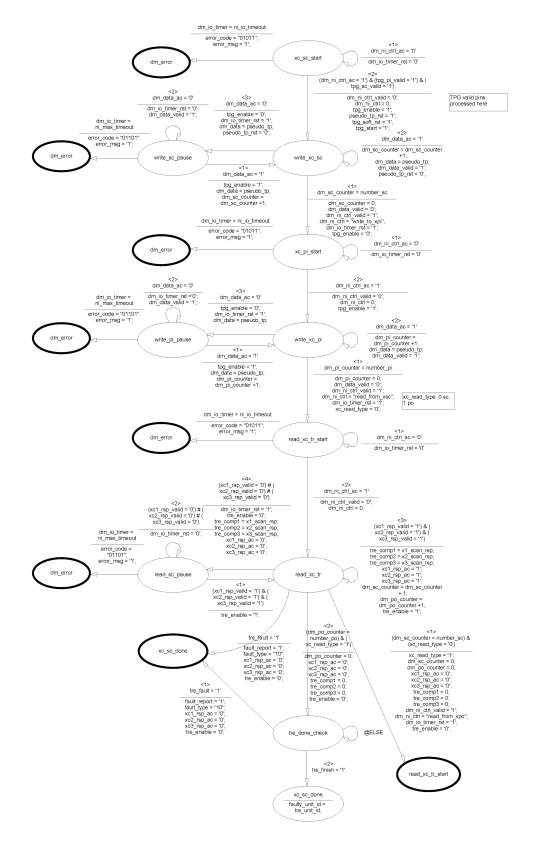

|   | 5.5 | Design  | of the DM-FSM                                            | 123 |

|   |     | 5.5.1   | Functional overview                                      | 123 |

|   |     | 5.5.2   | DM-FSM I/O and communication protocol                    | 124 |

|   |     | 5.5.3   | FSM architecture                                         | 127 |

|   | 5.6 | Design  | of the DM-TRE                                            | 135 |

|   | 5.7 | Design  | of the DM Network Interface (DM-NI)                      | 139 |

|   |     | 5.7.1   | DM-NI overview                                           | 139 |

|   |     | 5.7.2   | DM-NI architecture                                       | 141 |

|   |     | 5.7.3   | DM-NI simulation results                                 | 142 |

|   | 5.8 | A depe  | endable DM                                               | 144 |

|   | 5.0 | Conclu  | isions                                                   | 146 |

### CONTENTS

| 6            | Imp                    | olemen  | tation, Verification and Experimental Results                    | 147   |

|--------------|------------------------|---------|------------------------------------------------------------------|-------|

|              | 6.1                    | FPGA    | A-based implementation and verification                          | . 150 |

|              |                        | 6.1.1   | Introduction                                                     | . 150 |

|              |                        | 6.1.2   | DM Verification                                                  | . 152 |

|              |                        | 6.1.3   | DM verification with a tailored MPSoC framework on FPC           | A157  |

|              | 6.2                    | ASIC    | Realization of a Dependable Homogeneous MPSoC $ . $              | . 165 |

|              |                        | 6.2.1   | DM in the Reconfigurable Fabric Device (RFD) $\ \ldots \ \ldots$ | . 165 |

|              |                        | 6.2.2   | The General Stream Processor platform                            | . 168 |

|              | 6.3                    | Measu   | rement results of the GSP platform                               | . 168 |

|              |                        | 6.3.1   | The dependability software                                       | . 168 |

|              |                        | 6.3.2   | Test of the DM operations in the RFD                             | . 171 |

|              |                        | 6.3.3   | Test of the XTW fault emulation function                         | . 173 |

|              |                        | 6.3.4   | Full dependability test without applications                     | . 174 |

|              |                        | 6.3.5   | Full dependability test at application run-time                  | . 177 |

|              | 6.4                    | Deper   | ndability test power evaluation                                  | . 180 |

|              |                        | 6.4.1   | CMOS circuit power dissipation                                   | . 180 |

|              |                        | 6.4.2   | Estimation of the dependability test power dissipation .         | . 182 |

|              |                        | 6.4.3   | Power measurement result and discussion                          | . 184 |

|              | 6.5                    | Deper   | ndability improvement                                            | . 185 |

|              |                        | 6.5.1   | Reliability improvement                                          | . 186 |

|              |                        | 6.5.2   | Availability and maintainability improvement                     | . 186 |

|              |                        | 6.5.3   | Cost of dependability                                            | . 188 |

|              | 6.6                    | Concl   | usions                                                           | . 188 |

| 7            | Cor                    | ıclusio | n                                                                | 191   |

|              | 7.1                    | Gener   | ral conclusions                                                  | . 191 |

|              |                        | 7.1.1   | MPSoC dependability attributes and measures                      | . 192 |

|              |                        | 7.1.2   | MPSoC dependability enhancement and costs                        | . 192 |

|              |                        | 7.1.3   | Our dependability approach and implementation                    | . 193 |

|              | 7.2                    | Futur   | e work                                                           | . 195 |

| $\mathbf{A}$ | $\mathbf{D}\mathbf{M}$ | I-FSM   | Design Using the StateCAD Software                               | 197   |

| Bi           | bliog                  | raphy   | •                                                                | 203   |

# List of Acronyms

**API** Application Programming Interface

**ASIC** Application Specific Integrated Circuit

ATE Automatic Test Equipment

**ATPG** Automatic Test Pattern Generation

BIST Built-In Self-Test

**CFR** Constant Failure Rate

**CG** Clock Gate

CMOS Complementary Metal-Oxide Semiconductor

**CPU** Central Processing Unit

CRISP Cutting edge Reconfigurable ICs for Stream Processing

CUT Circuit Under Test

**DfDEP** Design for Dependability

**DfT** Design for Test

**DM** Dependability Manager

**DMR** Dual Modular Redundancy

**EM** Electromigration

#### LIST OF ACRONYMS

FC Fault Coverage

**FIT** Failures In Time

FPGA Field Programmable Gate Array

**FSM** Finite State Machine

GNSS Global Navigation Satellite System

GPD General purpose Processor Device

**GPP** General Purpose Processor

**GSP** General Stream Processor

GUI Graphical User Interface

**HCI** Hot Carrier Injection

**HW** Hardware

I/O Input / Output

IC Integrated Circuit

IIP Infrastructural IP

IM Infant Mortality

IP Intellectual Property

LFSR Linear Feedback Shift Register

MCP Multi-Channel Ports

MDT Mean Down Time

MISR Multiple-Input Signature Registers

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MPSoC Many-Processor System-on-Chip

MTBF Mean Time Between Failure

MTTD Mean Time To Detect

MTTF Mean Time To Failure

MTTR Mean Time To Repair

**NBTI** Negative Bias Temperature Instability

**NI** Network Interface

NoC Network-on-Chip

**PBTI** Positive Bias Temperature Instability

PCB Printed Circuit Board

PI Primary Inputs

PLL Phase-Locked Loop

**PO** Primary Onputs

**PRPG** Pseudo-Random Pattern Generator

**QoS** Quality-of-Service

**RFD** Reconfigurable Fabric Device

SBST Software Based Self-Test

SIM Scan Input Multiplexer

SIU Surround Input Unit

SoC System-on-Chip

**SOU** Surround Output Unit

**SRAM** Static Random Access Memory

**SW** Software

#### LIST OF ACRONYMS

**TAM** Test Access Mechanism

TDDB Time Dependent Dielectric Breakdown

TMR Triple Modular Redundancy

**TPG** Test Pattern Generator

TRE Test Response Evaluator

TSG Test Stimuli Generator

VC Virtual Channel

VCH Virtual Channel Handlers

VHDL VHSIC Hardware Description Language

VLSI Very Large Scale Integration

**XTW** Xentium Tile Wrapper

# Chapter 1

# Introduction

For decades, computing systems have been widely used in almost all fields of human activities, both for production and for everyday life. Dependable computing architectures are of crucial importance for mission-critical or human-life critical applications such as aerospace and automotive industry, railway transport, defence systems or banking and stock-trading systems. Undependable computing systems can not only cause financial and environmental disasters but also loss of human life. For example, the Tokyo Stock Exchange has experienced a malfunction in its computer servers due to a hardware failure in February 2012. The failure has knocked out trading on the Japanese stock market four hours [Bloo 12]. In July 2011, two high-speed trains collided with each other in Wenzhou, China, which resulted in 40 people killed and at least 192 injured. The cause of the accident were failures in the signalling and control systems due to lightning strike [Chin 11].

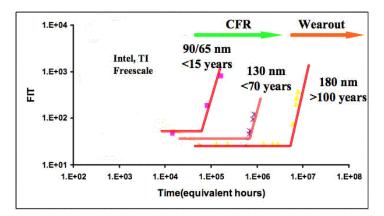

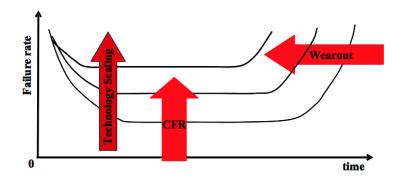

Apparently, the characteristics of a dependable system are the continuous operation and the capability to deal with possible faults. However, the shrinking dimensions of MOS transistors (less than 22nm) and the increasing complexity of semiconductor devices (e.g. Intel Itanium processor with 3.1 billion transistors [Toms 12]) have worsened the dependability of modern ICs. For instance, previous studies [Whit 08b] indicated that the wear-out failures appear much earlier in products using newer CMOS technology nodes as compared to those using older nodes (see Figure 1.1 (a)). Meanwhile, the constant failure rate (CFR) and chance of infant mortality (IM) also increase as the technology scales down

#### 1. INTRODUCTION

(Figure 1.1 (b)).

An apparent trend in the semiconductor industry is to integrate many components and functional blocks into a single chip to meet the area and power-consumption requirements of target applications. An increasing number of applications also need more than one processing core for complex computations. Many-processor system-on-chip (MPSoC) is becoming a popular solution for these applications. Experts have predicted that MPSoCs with more than a thousand processing cores may come to market in the near future [Bork 07]. How to guarantee the dependability of an MPSoC with billions of transistors is attracting increased research interests.

The source of the reliability issues in an MPSoC includes transient faults caused by alpha particles or cosmic rays and permanent faults caused by material aging or system wearout effects. Below the 45nm technology node, negative effects such as negative bias temperature instability (NBTI), hot carrier injection (HCI) or time dependent dielectric breakdown (TDDB) are becoming increasingly noticeable [Whit 08a]. These effects can cause the degradation of internal components and accelerate the occurrence of permanent faults [McPh 06]. A single transistor defect can result in the malfunction or complete failure of an MPSoC. For example in 2011, a major CPU provider has called back a processor product due to a transistor hard failure in the chipset of the processor and suffered a financial loss of about 1 billion US dollars as a result of this [Cnet 11]. More catastrophic consequences could be expected if these processors would have been shipped to customers and used for critical applications. Therefore, we explore in this thesis methods to enhance the dependability of MPSoCs and how to deal with permanent failures during its life time.

# 1.1 Research problem statement

As MPSoCs are playing an important role in modern safety-critical applications, the dependability of these applications is of crucial importance. In this thesis, the dependability of MPSoCs and approaches for dependability enhancement have been studied. The main research problems addressed in this thesis are:

(a) Normalized manufacturers data on product level failure rate as a function of technology nodes. Below the nodes, the product life time (in equivalent hours) is depicted.

(b) Product failure rate trend as technology scales down: chances of infant mortality increases, constant failure rate goes up and possible wear-out failures will occur earlier.

**Figure 1.1:** The worsening product dependability as technology scales down [Whit 08b]

#### 1. INTRODUCTION

- What are the important attributes of a dependable MPSoC and how to measure its dependability in a quantative way?

- What are the possible approaches to enhance the dependability of an MP-SoC? What are the costs of the chosen dependability approach in terms of performance and resource (silicon area/energy) overhead?

- How does the implementation of the chosen dependability approach in silicon improve dependability and how can its effectiveness be evaluated using experiments and actual measurement results.

## 1.2 The CRISP project

Due to the rapid development of all kinds of standards, protocols and algorithms, application providers tend to welcome reconfigurable platforms to implement their applications. A reconfigurable platform offers a convenient solution to update or change the hardware platform in case the application requires flexibility. Field Programmable Gate Arrays (FPGAs) have been very well known for their flexibility and the ease of fast prototyping. However, FPGAs are usually inferior in terms of speed, area and power consumption when compared to their counterparts, the application-specific integrated circuits (ASICs) [ASIC 07]. Hence, there is an increasing need for reconfigurable ICs which combine the flexibility of FPGAs and the performance advantage of ASICs [Heys 04].

The Cutting edge Reconfigurable ICs for Stream Processing (CRISP) project (FP7, ICT-215881) aims to develop a scalable, dependable and reconfigurable many-processor system-on-chip (MPSoC) for a wide range of data streaming applications [CRISP 07]. Stream processing is a digital signal processing technique which is widely used for wireless communication, multimedia and intelligent antennas, etc. Two examples of streaming applications which have been used in the CRISP project are digital radar beamforming and Global Navigation Satellite System (GNSS) reception.

It is the goal of the CRISP project to implement a reconfigurable massive multi-core platform, being a General Stream Processor (GSP), for tomorrow's streaming applications [Burg 11]. One of the important features which distinguishes the GSP from other digital signal processors is that measures have been taken such that during design-time and run-time its dependability can be enhanced [Ter 11]. Dependability approaches such as static and dynamic detection and localization of faults and dynamically circumventing identified faulty hardware have been proposed, implemented and validated in the CRISP project [Zhan 11]. An example application (radar beamforming) has been chosen for defining the boundary conditions (dependability specifications) of the dependability approach and for dependability attributes evaluation [Zhan 09b]. This thesis partly describes the dependability approach of the CRISP project.

### 1.3 Contribution of this thesis

The first contribution of this work is a study on MPSoCs from a dependability perspective. Important dependability attributes such as reliability, availability and maintainability of an MPSoC are carefully studied in this thesis. A dependability matrix is proposed to evaluate the dependability parameters and determine the cost for dependability enhancement.

The second contribution of this work is the proposed dependability approach. First a review of existing MPSoC dependability improvement methods has been carried out. Theoretically, the dependability of an MPSoC can be enhanced by determining faulty parts via a self-test and eliminating any faults in the MPSoC and remapping the tasks in the application to fault-free resources. Hence the dependability approach proposed in this thesis comprises of two major parts: self-test and self-repair. Periodic structural scan-based tests can be performed on the processing cores using the NoC as a test access mechanism. Thanks to the homogeneous structure of the target MPSoC, test responses can be compared with each other to determine a faulty core by carrying out majority-voting. The major innovation of our work is to carry out dependability tests via the NoC at run-time. This ensures a high level of availability of the target platform. The dependability of the network-on-chip (NoC) in the MPSoC is a prerequisite of the proposed dependability approach and the NoC is tested by using functional tests.

#### 1. INTRODUCTION

The third contribution is the design of an infrastructural IP dependability manager. The dependability manager consists of three major building blocks being a test-pattern generator, a test-response evaluator and an FSM for control of the test process. The dependability manager has been designed as generic as possible and a tool-chain has been developed to automate the design process. A new design can be automatically generated given the test-pattern set of the target processor tile under test and detailed requirements such as fault coverage or maximum silicon-area.

To validate the feasibility of the dependability manager architecture, it has been synthesized using UMC 90nm CMOS technology and the resulting netlist has been thoroughly simulated with an MPSoC framework as a testbench. Lastly, a nine-core MPSoC with our dependability infrastructures has been fabricated using the UMC 90nm CMOS technology. The developed dependability software successfully runs on the platform and the complete dependability test flow has been validated through measurement results on a prototype chip.

### 1.4 Outline of this thesis

As predicted by Moore's law, the size of MOSFET transistors continues to shrink and the density of integrated circuits increases already for half a century. In Chapter 2, this down-scaling trend in CMOS technology and system design will be further elaborated. In addition, its impact on system dependability will be discussed. Background information such as the production and life cycle of semi-conductor devices, basics of integrated circuit testing and faults which can occur during lifetime of a chip will also be briefly discussed.

In Chapter 3, the basic principle of system dependability will be introduced. Important dependability attributes such as reliability, availability and maintainability will be examined in detail. Moreover, we will discuss the possible options to enhance system dependability in order to satisfy the dependability requirements of a specific application.

Chapter 4 presents our proposed dependability approach to enhance the dependability of an example MPSoC. The basic idea is to perform a dependability test on chip at runtime for fault detection and to use proper resource management software for system reconfiguration. The design of essential infrastructures and software needed by the dependability test are discussed in detail.

The most critical part of our dependability approach is an infrastructural IP called the dependability manager. Its responsibilities include test-vector generation, test-response evaluation and the control of the complete dependability test process. The architecture of the dependability manager and the design of its key building blocks will be described in detail in Chapter 5.

In Chapter 6, the design flow, verification and implementation details of an MPSoC equipped with our dependability manager are presented in detail. The design has finally been implemented as a UMC 90nm nine-core MPSoC with dependability enhancement features. Measurement results on a prototype chip showed the correctness of the dependability infrastructure design and we have validated the effectiveness of our dependability approach.

Chapter 7 concludes the thesis with a summary of the presented work and gives some suggestions for future work.

### 1. INTRODUCTION

# Chapter 2

# Trends in CMOS Technology, System Design and Dependability Challenges

ABSTRACT - In this chapter, the impact of CMOS scaling on system dependability will be introduced. First, a brief overview of the terminology, principles and mechanisms related to semiconductor faults and defects will be given. Typical aging effects which occur during lifetime of a chip and their influence are discussed. Furthermore, some existing test methods related to our dependability test in later chapters will be briefly revisited.

# 2.1 Dependability challenges

## 2.1.1 CMOS scaling and complexity

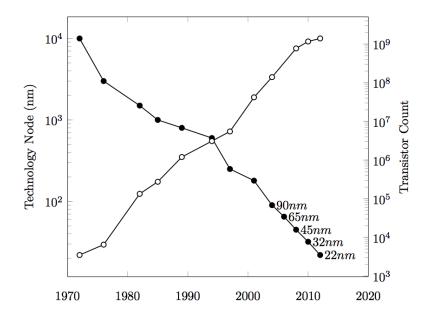

In the 1960s, it was predicted by Moore's law that the transistor density of integrated circuits will roughly double for every two years. As shown in Figure 2.1, the prediction has been accurate for half a century and is the de facto guideline for the research and development of the semiconductor industry since the late twentieth century. The continuous and aggressive shrinking of MOSFET dimensions resulted in a constant performance increase per unit silicon area and a decrease of the supply voltage. Nowadays, 20nm CMOS technology has been implemented

# 2. TRENDS IN CMOS TECHNOLOGY, SYSTEM DESIGN AND DEPENDABILITY CHALLENGES

in industry and 11nm technology is likely to follow in the year 2016. It was predicted in the 2011 International Technology Roadmap for Semiconductors (ITRS) report that the transistor gate length will scale below 10nm and new structures such as multi-gate MOSFETs will be implemented within 10 years [ITRS 11].

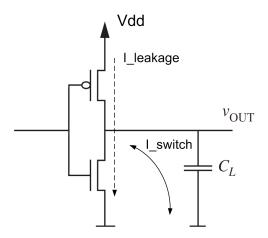

Figure 2.1: Moore's law: CPU transistor count and technology nodes

The endeavour to make smaller transistors has resulted in allowing more system complexity and faster devices. However, the down-scaling of transistor parameters is negatively impacting the reliability of the building blocks of an integrated circuit. For example, the continuous reduction of the thickness of the MOS transistor gate oxide layer leads to a dielectric as thin as 1nm, which is equivalent to 3-4 monolayers of atoms. The ultra-thin gate oxide increases the leakage current as well as the chance of a gate dielectric breakdown. As silicon-based oxide has reached its limit, new materials have been adopted to maintain the scaling demand of industry. Starting from the 45nm technology node, high-K transition metal oxide has been used as dielectric material and metal gates adopted instead of polysilicon gates. New structures such as FinFETs [Hu 12] and extremely thin silicon-on-insulator (ETSOI) transistors are required to maintain the down-scaling trend continuing beyond the 15nm node [Stat 10].

The use of new materials and structures changes the behaviour of well-known failure mechanisms such as time-dependent dielectric breakdown (TDDB) [Whit 08a] and also bring in new reliability concerns e.g. random telegraph noise (RTN). In the ITRS 2011 report [ITRS 11], it is already regarded as a major challenge to sustain current IC reliability level with future devices.

Another direct consequence of the scaling of the MOSFET transistor is the increased integration density. The ever increasing need for higher computation power leads to more and more transistors and interconnects implemented into the same silicon area, which naturally results in more potential fault sites.

On the other hand, the technology advances enabled the integration of a number of processing cores into a single silicon die, which is known as the multiprocessor or many-processor system-on-chip (MPSoC). Today, the MPSoC has been widely adopted for desktop as well as embedded and mobile products. Industry expects a single chip with more than a thousand processing cores to be on the market in the near future [Bork 07]. Increasing dependability challenges as a result of the growing structural complexity and strict timing schedule of multi/many-core interaction have already been shown [Axer 11]. Meanwhile, the flexible structure of the MPSoC makes it possible to use fault detection and resource reconfiguration mechanisms to tolerate a certain number of faults and enhance system dependability as will be shown later.

In conclusion, the continuous advances of semiconductor technology have brought enormous dependability challenges. At the same time, new possibilities are also emerging from the MPSoC domain for the enhancement of dependability.

## 2.1.2 Application reliability and availability requirements

Nowadays, more and more high-end IC products are being used in a harsh environment for life or mission critical applications, such as automotive, military, aerospace and medical [Hinc 10, Rabb 10]. Different from desktop or normal mobile applications, much more severe external stress factors such as temperature, shock and radiation are often expected in these applications. For example, a growing trend in the aviation industry is to replace traditional centralized engine controllers with distributed control systems. This replacement can result in much

# 2. TRENDS IN CMOS TECHNOLOGY, SYSTEM DESIGN AND DEPENDABILITY CHALLENGES

simpler interconnections and save hundreds of pounds of aircraft weight. Consequently the control electronics are placed closer to the engine and must function correctly with a temperature range from  $-55\,^{\circ}\text{C}$  to  $200\,^{\circ}\text{C}$ . The automotive industry is another example requiring an increasing number of high-temperature electronics as mechanical and hydraulic parts are being replaced by electromechanical systems. For instance, the transmission controller and wheel sensors need to work with an ambient temperature of around  $200\,^{\circ}\text{C}$ . And the exhaust sensors must function properly at a peak temperature of  $850\,^{\circ}\text{C}$  [Wats 12].

There are also applications which require very low system down-time (high availability requirement) such as ICs used for telecommunication base stations, banking, trading and stock-market servers. For example, many multinational continuous process manufacturing companies need to manage worldwide operations and business transactions from clients and suppliers all day everyday. Stock trading and investments companies which manage billions of U.S. dollar assets can tolerate almost zero downtime of their IT infrastructure. Another example is the Chinese online train-ticket sale system. In recent years before the Chinese Spring Festival, the train-ticket online sale website must be able to handle over five million concurrent transactions for weeks. A few minutes unavailability of the website server will cause catastrophic social and political consequences. As such, reliability and availability are becoming major requirements in electronic systems when used in these particular applications.

# 2.2 Production and life cycle of semiconductor devices

# 2.2.1 A brief introduction to semiconductor manufacturing

The semiconductor manufacturing flow comprises of a number of closely related stages. The flow begins with circuit design and wafer production. The target circuit is implemented during wafer fabrication. Then it is assembled, packaged and tested before the final IC product is delivered to the customer. Each manufacturing stage involves a number of processes. Hundreds of process steps are required in the complete flow. For example, wafer fabrication includes oxidation, deposition, lithography and etching; wafer testing consists of wafer sorting and laser repair, etc.

Due to the complexity of technology, the need for highly precise process steps and the vulnerability to contamination, defects can be expected in every stage of the semiconductor manufacturing chain. Defects can cause faults and failures in IC products. If detected during the manufacturing flow, chip defects will result in yield loss. If faults and failures occur after the chips have been shipped to customers, they can cause system malfunction and damage the reputation of the semiconductor manufacturer [Bush 05]. In the next section, some basic taxonomy and terms related to defects are introduced.

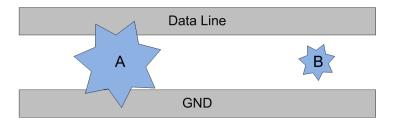

### 2.2.2 Taxonomy and terminology

In the semiconductor world, defect, fault and failure are often used to denote incorrect parts or behaviours in a device or a system. A defect is a physical flaw or imperfection which violates the design specification. The cause of defects can be incorrect manufacturing operation, material contamination during fabrication or structure wearout during the product life cycle. A defect is the root of a fault, but not all defects result in faults. For instance in Figure 2.2, conducting particles A and B are defects introduced during the wafer fabrication stage. Particle A can cause an unexpected short connection between the data line and the ground line. However, particle B will not cause such a problem. Thus a fault is the result of a critical defect which can cause unacceptable fluctuation of performance or incorrect functional behaviour.

Faults in semiconductor devices commonly fall into three main categories: permanent, intermittent and transient faults. Permanent faults are continuous and irreversible faults which persist regardless of time. Examples of permanent faults include missing material, bridging wires and broken oxide layers, etc. Intermittent faults are usually caused by internal parameter degradation or material instability. Intermittent faults often precede the occurrence of permanent faults as the degradation progresses. A gate dielectric soft breakdown is an example of

# 2. TRENDS IN CMOS TECHNOLOGY, SYSTEM DESIGN AND DEPENDABILITY CHALLENGES

Figure 2.2: Example of critical and non-critical defects

an intermittent fault. Transient faults are also known as random faults. They usually occur as a result of temporary environmental conditions, such as temperature variations, effect of high energy particles or electromagnetic interference. Most tests in digital circuits are based on permanent faults.

A fault in a system can make it fail to deliver the expected service. If a failure occurs in an IC, it can no longer comply with specified functions. The incorrect state and output generated during a system failure is sometimes also referred to as error. The terms mentioned above are similar but not interchangeable. Defects are physical and structural; errors are logical and functional. A fault is local whereas a failure is global.

### 2.2.3 IC life cycle and failure rate

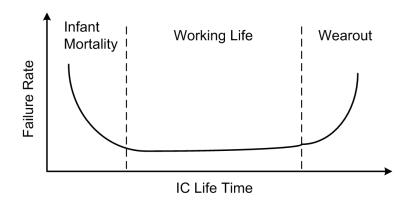

Three distinctive stages can be identified during the lifetime of an IC, being the infant mortality, working life and wearout stages. The probability an IC will fail in each stage is indicated by the *failure rate*. The failure rate  $\lambda(t)$  of an IC varies with time and exhibits the well-known bathtub curve as shown in Figure 2.3.

#### 2.2.3.1 Infant mortality

As Figure 2.3 shows, the curve begins with a high failure rate after manufacturing which gradually decreases. The infant mortality stage can last from weeks to as long as half a year. Infant defects are often caused by extremely marginal structures during the assembly process. These defects somehow passed the basic production test but can result in faults and failures shortly after. ICs at the infant mortality stage should not be shipped to customers in order to avoid field

Figure 2.3: Bathtub-shaped failure rate distribution during IC life time

failure and product return. Burn-in is an engineering method for screening out early failures in the factory before the products reach the customers [Kuo 84, Kim 09, Tsai 11]. During the burn-in process, a device is stressed under constant thermal and electrical conditions in order to accelerate the appearance of early failures. Other methods such as vibration, power and temperature cycling are also used to carry the chip through the infant mortality stage. Notice that in many non-critical ICs, burn-in is not done. Instead, IDDQ tests which measure the quiescent supply current are used to weed out potential reliability weaknesses.

#### 2.2.3.2 Working life

The main characteristic of the normal working life stage is the low and nearly constant failure rate (slight variation in practice). Faults will still occur at random spots in this timeframe but the chance is much smaller than in the infant mortality stage. The failure rate of this stage is commonly referred to by the term of Failures in Time (FIT) in the semiconductor industry. FIT is defined as the number of failures that can be expected in one billion ( $10^9$ ) device-hours of operation. One billion device-hours can be combinations like 1,000 devices for 1 million hours each or 1 million devices for 1,000 hours each, etc. For example, the failure rate  $\lambda(t)$  of a chip with 10 FIT is:

$$\lambda = \frac{10}{1 \times 10^9} = 1 \times 10^{-8} \text{ failures per hour}$$

(2.1)

# 2. TRENDS IN CMOS TECHNOLOGY, SYSTEM DESIGN AND DEPENDABILITY CHALLENGES

The expected average time before a component or system fails after initialization is defined as the mean time to failure (MTTF). For the majority of electrical systems with a constant failure rate, the failure distribution is exponential during its working life. This causes the MTTF to be the reciprocal of the failure distribution rate  $\lambda(t)$ . To continue with the above example, the MTTF of the system is:

$$MTTF = \frac{1}{\lambda} = 1 \times 10^8 \text{ hours}$$

(2.2)

Some systems can repair their failure and return to their normal function. Such a system is defined as a repairable system [Asch 84]. The time frame after the occurrence of a system failure until it is fully restored is defined as the system down-time. Mean time between failures (MTBF) is used to denote the expected average time between two successive failures of a system. MTBF is an important concept in reliability engineering and should not be confused with MTTF. MTBF is only applicable for repairable systems whereas MTTF is commonly used for non-repairable systems which can fail only once. In some literature MTBF is referred to as the mean time before failures. Only in this case, the MTBF is equivalent to MTTF. Note that in this thesis, MTBF is always defined as the mean time interval between two system failures.

#### 2.2.3.3 Wearout

Ultimately, the failure rate of an IC will start to increase as its internal parts begin to fatigue and wearout. The occurrence of the wearout stage of an IC depends on many factors such as technology, heat, input signals (work load in case of a processor) and power-supply stress conditions. Wearout defects such as electromigration or time-dependent dielectric breakdown often first appear as intermittent faults and then gradually become permanent faults and cause system failure. Several typical wearout mechanisms will be briefly introduced in following sections.

# 2.3 Faults occurring during IC lifetime

The aggressive technology scaling has resulted in an extremely high level of device density and computational performance boost as well as accelerated circuit degradation and wearout during their operational life time. Consequently, chips which have passed the final production test can fail during their life cycle. The major degradation mechanisms of semiconductor microelectronic devices are negative/positive bias temperature instability (NBTI/PBTI), gate oxide breakdown, also known as time-dependent dielectric breakdown (TDDB), hot carrier injection (HCI), and electromigration (EM). These mechanisms are briefly reviewed below.

### 2.3.1 Negative/positive bias temperature instability

Negative bias temperature instability is a wearout mechanism mainly observed in p-channel MOS transistors since they usually operate with negative gate-to-source voltage. NBTI is accelerated by elevated temperature and voltage levels and manifests itself as an increase in threshold voltage and a decrease of the drain current and transconductance [Schr 03]. As a result of its adverse impact on the critical parameters of the PMOS transistor, NBTI has become a serious CMOS reliability concern.

Recent research suggested NBTI is physically caused by two tightly coupled mechanisms: interface state generation and holes trapping in the oxide traps [Gras 09]. Fast advances in CMOS processing technology did not alleviate the NBTI effect, instead, they made it worse. For example, nitrogen was incorporated into MOSFET gate oxide to reduce the gate leakage current. However, the introduction of nitrogen turns out to accelerate the NBTI degradation. In addition, transistor size down-scaling resulted in stronger internal electric fields and higher temperature, which also aggrevated the NBTI effect.

The positive bias temperature instability (PBTI) on the other hand affects n-channel MOS transistors in the case they are positively biased. It has a similar mechanism as NBTI and can also negatively impact transistor reliability. In practice, NBTI is the dominant degradation problem. Delays faults will develop as a result of the BTI effect.

# 2. TRENDS IN CMOS TECHNOLOGY, SYSTEM DESIGN AND DEPENDABILITY CHALLENGES

### 2.3.2 Hot carrier injection (HCI)

Carriers (electrons or holes) are able to gain substantial kinetic energy as they travel through a region of a high electric field. For instance, if current flows through the source-drain channel in a MOSFET, carriers can become sufficiently energetic to be *hot*, which is a term used to measure their energy level instead of temperature. Hot carriers can gain so much energy that they are injected into the gate oxide bulk of the MOSFET via scattering or impact ionization [Terr 85, Maha 00, Here 88].

The injection of hot carriers into the oxide can cause various physical damage and change the characteristic parameters of a MOSFET, such as a shift of its threshold voltage as a result of interface-state generation. A device suffering from HCI will eventually fail as defects accumulate. HCI has been regarded as a critical reliability concern which will adversely impact the reliability of semiconductor devices.

The HCI effect is strongly affected by the internal electric field distribution of a transistor. As the down-scaling of the supply voltage is far slower than the shrinking of the channel length and oxide thickness, the internal electric field intensity continuously increases and the reliability issues caused by HCI become worse. It will result at some stage in delay faults.

# 2.3.3 Time-dependent dielectric breakdown (TDDB)

Dielectric breakdown is the irreversible change of the dielectric property of the gate oxide layer of a MOSFET [Bern 06]. As the dielectric layer of a MOSFET is subject to electric field stress, structural degradation slowly develops in the oxide. As a consequence, the electrical property of the dielectric will gradually change until a hard breakdown takes place. This form of dielectric breakdown is referred to as time-dependent dielectric breakdown.

The general mechanism of TDDB is that under the stress of an electric field, charges are trapped in various parts inside the oxide layer and at its interface. As a result, stress induced leakage current (SILC) is produced, which flows through the dielectric material and creates a heating effect. The heat accumulation can gradually cause thermal damage to the oxide and increase the density of charge

traps (soft breakdown). This positive feedback loop will eventually cause a permanent conductive path within the dielectric, which shorts the gate with the substrate material or the source/drain and results in a faulty transistor [Stat 02]. In such a case, a hard breakdown, i.e. a permanent fault occurs.

The rate of the TDDB defect generation is proportional to the current density flowing through the oxide layer, which is accelerated by the increase of supply voltage and temperature. As a result of the down-scaling of device dimensions, the thickness of the gate oxide continuously decreases, which also leads to an early dielectric breakdown.

#### 2.3.4 Electromigration (EM)

Unlike the previous three wearout effects, electromigration does not take place within the MOS transistors. Instead, the degradation is found in the chip's metallization. Electromigration refers to the transport of metal atoms in the metal thin-film as a result of the flow of electric current. The movement of the metal atoms can cause depletion of the metal material in some places (e.g. cathode side) and accumulation in other places (e.g. anode side). Consequently, high resistances or broken wires can result from the EM effect, which will lead to time-related faults or permanent open wire faults. On the other hand, accumulation of metal atoms can cause permanent shorts between interconnections.

In [Blac 69], the determining factors of the EM-related MTTF has been concluded: MTTF<sub>EM</sub> is proportional to the area of the cross-section of the wire; MTTF<sub>EM</sub> also has an inverse relationship with the current density through the wire. As device features continuously shrink and wire current density stays high, we arout of wires due to EM will inevitably result in various permanent faults in a chip and continue to be a serious chip reliability threat.

#### 2.3.5 Fault models

Faults caused by the former degradation effects are generally known as *aging* faults. Typical consequences of aging faults in digital circuits can either be logic faults or delays faults. Logic faults are caused by transistors or wires which are open or shorted to (stuck at) logic 1 or 0. A delay fault means that the delay of

## 2. TRENDS IN CMOS TECHNOLOGY, SYSTEM DESIGN AND DEPENDABILITY CHALLENGES

one or more paths exceeds the clock period. It can result in incorrect logic values under a specified clock frequency. Notice that by lowering the clock rate, one can eliminate some of the delay faults. All the aging effects introduced earlier can first lead to intermittent delay or logic faults, and then eventually progress into permanent faults [Rade 13].

In this thesis, the intermittent faults are treated as permanent faults as well because the approaches we adopt for testing permanent faults remain effective when the intermittent faults develop into permanent ones. The stuck-at fault model has been widely used for permanent faults detection and diagnosis in a logic circuit. Thus it will be used as the fault model in our dependability test which will be introduced in the following chapters.

#### 2.4 Basics of testing

The continuous down-scaling trend and the increasingly complex manufacturing process of integrated circuits both result in higher chances of defects in semiconductor products. A single defect can easily lead to a fault in a component and eventually in a complete failure of a billion-transistor MPSoC. Thus testing is required to guarantee that only fault-free devices are delivered to the end users.

Different from design verification, manufacturing testing is not intended to verify the correctness of the design itself but to check the soundness of the manufacturing process. Note that the result of testing can be used as more than just a device pass/fail indication. It can also be used as the basis of fault diagnosis, which tries to locate the defects and origin that caused the fault and helps to eliminate this in order to improve the production yield. In fact, testing can also be performed during the life cycle of an integrated circuit by means of e.g. built-in self-test (BIST) [Bush 05]. As such, the correctness of an IC can be periodically checked during its working life and repair operations could be enabled in case of any faults. This is particular useful for applications with the requirement of a high level of dependability.

Tests performed after the wafer fabrication generally fall into two categories: parametric tests and functional/structural tests. Examples of parametric tests are DC and AC tests which are carried out subsequently to detect potential electrical

and timing problems before the test of the logic functions of the IC [Bush 05]. The basic idea of functional/structural test is to apply specific test stimuli (test vectors or test patterns) to the circuit under test (CUT) and to separate the good devices from the faulty ones by examining their test responses. If the test responses of a CUT do not agree with those of a known-good circuit, the target CUT is considered to be faulty. For an n-input combinational CUT, there are  $2^n$  possible combinations of test vectors in total, which is usually too large to test for a modern circuit with many inputs. In practice, only a subset of all the test vector combinations are used to test a circuit. One possibility (denoted functional test) is to use the input combinations if a CUT operates in a real system as test vectors. One can get an indication of the CUT's correct functional behaviors using this method. However, the thoroughness (fault coverage) of functional test is often quite limited. In addition, there is no real quantitative measure of the defects which can be detected out of the total set of defects in the case of a functional test.

As a result the manufacturing test uses the structural information of the CUT instead of its designed functionality. In structural testing, faults can be regarded as the deviation of logic values caused by critical structural defects. Various fault models such as single stuck-at (SSA) fault, bridging fault and delay fault have been established to represent the consequence of defects in a CUT. As such, a physical defect can be modeled at the logic level. Take a 4-input AND gate as an example, if any input pin is shorted with the ground line, a stuck-at-0 fault model can be used to model the fault. The logical consequence of the defect is that the output level of the AND gate is fixed to a logic zero. As different defects can yield the same logical fault, one structural test vector is capable of detecting thousands of faults in a large circuit, which makes it a very efficient and effective approach. The effectiveness of a structural test can be measured by its fault coverage, which is defined as:

Fault coverage =

$$\frac{\text{Number of detected faults}}{\text{Number of all possible faults}}$$

(2.3)

The goal of test pattern generation is to find a minimum set of test vectors which can detect all the possible faults of a chosen fault model(s), namely to

## 2. TRENDS IN CMOS TECHNOLOGY, SYSTEM DESIGN AND DEPENDABILITY CHALLENGES

achieve a 100% fault coverage. The test pattern fault coverage is calculated by performing fault simulations. A fault simulator can emulate target faults in the CUT, apply test vectors to its input and compare the simulated test responses with the reference responses. In this way, it can determine which faults are detected by a given set of test vectors. Mature commercial tools (e.g. TetraMAX from Synopsys) are available for both automatic test pattern generation (ATPG) and fault simulation. Using the netlist of the CUT as an input, one can obtain its test patterns which meet a specific fault coverage requirement.

However, the complexity of ATPG algorithms and the huge number of fault sites require excessive computational power. As a result, design for test (DfT) approaches are often adopted at the design phase, which can greatly reduce the computational requirement. DfT efforts aim to increase the controllability (setting a certain node in the CUT to a desired value) and observability (observing the logic value of an internal node) of the target circuit. Typical DfT examples are scan path and core-wrapper design and insertion. In addition to the increase of ATPG efficiency, DfT can also greatly enhance ATPG fault coverage. In this thesis, several DfT techniques have been adopted to help enhancing the dependability of a target MPSoC. Details of DfT architectures, test application and scheduling will be discussed in Chapter 4. Test vector generation will be covered in Chapter 5.

#### 2.5 Conclusion

The continuous down-scaling trend of CMOS technology nodes leads to even smaller transistor dimensions and as a result much more complex systems. Increasingly aging faults as a result of various degradation effects will occur during the life time of an IC. As a consequence, permanent logic and delay faults will appear much earlier than before. The increased complexity has enabled the introduction of multi-processor SoCs. This offers new possibilities for dependability enhancement via on-chip replacement of faulty processors. As an increasing number of advanced ICs are being used for life/safety-critical applications, their dependability requirements must be treated carefully. Conventional structural test methods for testing stuck-at faults can be adapted for permanent fault detection

as part of our dependability approach. More details will be given in subsequent chapters.

# 2. TRENDS IN CMOS TECHNOLOGY, SYSTEM DESIGN AND DEPENDABILITY CHALLENGES

## Chapter 3

## The Dependable MPSoC Concept

ABSTRACT - As indicated in Chapter 2, the continuous downscaling trend of MOS transistors has led to unreliable building blocks for an integrated circuit. The question how to make a dependable MPSoC boils down to how to build a dependable system using undependable components. The term dependable IC has been used in various occasions without a clear definition. In this chapter, a first step is made to analyze and measure the dependability of MPSoCs in a quantitative way.

This chapter is organized as follows. In Section 3.1, the definition of a dependable computing system is introduced. In Section 3.2 and 3.3, three main attributes of a dependable MPSoC are examined in detail. A theoretical analysis on the enhancement of each attribute is also given. Section 3.4 presents our design for the dependability concept as well as the design-space exploration to be used for the design of a dependable MPSoC.

Parts of this chapter have been presented at the 2010 International Symposium on System on Chips, Tampere, Finland [Ter 10].

# 3.1 Introduction into dependable computing systems

Five fundamental characteristics of a computing system were concluded in [Aviz 04], namely functionality, usability, performance, cost and dependability. The definition of computer system dependability has been evolving for several decades. Various definitions of dependability exist, with emphasis on different aspects of interest. Historical definitions of dependability have undergone a change of focus from the capability of system operation to successful task accomplishment [Parh 88]. The International Federation for Information Processing (IFIP) work group 10.4 on dependable computing and fault tolerance defined dependability as:

• The trustworthiness of a computing system which allows reliance to be justifiably placed on the service it delivers [IFIP 69].

Whereas the International Electrotechnical Commission (IEC) provided its definition of dependability as:

• a collective term used to describe the availability performance and its influencing factors: reliability performance, maintainability performance and maintenance support performance [IEC 12].

Based on the definitions given in previous studies, we adopt the following definition of dependability in this thesis:

• The justifiable confidence that a computing system can perform its specified functions and deliver its specified services in time under given operational and environmental conditions.

In contrast to a dependable system, an undependable computing system is one that operates too slow, performs incorrect functions or delivers incomplete services. System functions and promised services can be accurately specified by the system provider in a similar way as an Internet service provider can promise a service level agreement (SLA) to their users. The notion of dependability presented above is a general description of system characteristics in a non-quantitative way. Dependability attributes such as reliability, availability, maintainability, safety and confidentiality can be used to quantitatively measure the dependability of a computing system. In the scope of MPSoC dependability, three main dependability attributes reliability, availability and maintainability are studied in detail in the following sections. As safety and confidentiality are strongly application-scenario dependent, they will not be treated in depth in this thesis.

In addition to the dependability attributes, threats to dependability and means to improve system dependability have been summarized in previous studies [Aviz 04]. As indicated in Chapter 2, main threats to system dependability include defects which can result in faults and failures. Four important means to deal with these threats are fault prevention, fault tolerance, fault removal and fault forecasting.

- Fault prevention aims to prevent defects and faults from occurrence by e.g. use of more mature and reliable semiconductor processing technologies for IC fabrication.

- Fault tolerance is the endeavor to maintain system functions and avoid system failures in the presence of faults.

- Fault removal means to eliminate as many faulty parts in the system as possible.

- Fault forecasting means to estimate and determine whether faults are likely to take place in future by monitoring critical parameters such as temperature, current or voltage of the parts of interest.

Fault tolerance and fault removal are the main measures used in this thesis in order to improve system dependability. Note that fault removal in this research refers to the isolation of an entire processor core which contains faulty parts.

#### 3.2 MPSoC reliability

#### 3.2.1 The reliability function

Reliability is, by definition, the ability of a system to correctly perform specified functions under designated conditions for a specific period of time [IEC 07]. It can be determined by the metric of the probability that a system can correctly operate within a given time frame. The time frame is the mission time of a system, ranging from several years to several tens of years. If the mission time of a system is not clearly specified, the time frame can be the specified life time of the system. For example, a sedan can have a lifetime of 15 years and a truck 22 years.

The reliability of a system can be expressed as a reliability function R(t) for the mission time t. Similarly, the probability that the system will fail over the same time period can also be described as a function of time, i.e. the failure distribution function F(t). According to general probability theory [Bazo 04], it is obvious that:

$$R(t) = 1 - F(t) \tag{3.1}$$

As introduced in Chapter 2, the failure rate  $\lambda(t)$  is a parameter used as a metric for the occurrence of system failures. It is a variable which reflects the probability of a system failure at a certain moment t. A typical method to determine the failure rate of a semiconductor device is e.g. usage of accelerated stress tests on a set of samples of devices randomly selected from its production population. In a simplified approach, the calculation of the device failure rate can be performed as following: assume that we observe 10 out of 1,000 devices fail after the stress test finishes, it can be concluded that an individual device will fail with a probability of 1% by the end of the same test under the same conditions. The failure rate obtained from the sampled devices under accelerated stress test is then extrapolated to actual operating conditions to estimate the failure rate of the device when used in field operation. Different failure mechanisms and statistical acceleration models have been discussed in detail in previous studies [Bern 06] so they will not be further discussed in this thesis.

Previous studies have established the relation between R(t) and  $\lambda(t)$  [Bazo 04]

as:

$$R(t) = e^{-\int_0^t \lambda(t)dt} \tag{3.2}$$

The main characteristic of the normal operational life of a semiconductor device is the low and nearly constant failure rate (see Figure 2.3). We confine our reliability computations within this operational period and hence a constant failure rate value  $\lambda$  can be assumed. Equation 3.2 can be easily transformed as:

$$R(t) = e^{-\lambda t} \tag{3.3}$$

Hence, assuming a constant failure rate, common semiconductor devices have a reliability function in the form of a decreasing exponential function. The larger the failure rate  $\lambda$ , the faster the exponential function decreases.

As discussed in Chapter 2, the FIT (failures in time) number is commonly used in industry to specify the reliability of a semiconductor device. FIT represents the number of failures that can be expected in one billion device-hours' operation. It holds that:

$$R(t) = e^{-\lambda t} = e^{-FIT \times t \times 10^{-9}} \tag{3.4}$$

An example on how to calculate the reliability of chips with FIT information is given below. Suppose an IC manufacturing company produces a batch of chips with a FIT number of 100. To calculate the reliability of these chips in 10 years, i.e. 87,600 hours, Equation 3.4 is used:

$$R(87600) = e^{-100 \times 87600 \times 10^{-9}} \approx 99.1\%$$

Therefore the probability that these chips will correctly function after 10 years is about 99.1%.

It should be noted that the specified FIT number of mature modern IC is normally quite low, less than 100 or even less than 10 under commercial environmental and operational conditions. However, their actual failure rate will rise given severe environmental stress found in e.g. marine, aviation or space applications. Therefore in the following sections, exaggerated FIT values (e.g. 1,000 or even 10,000) are assumed in the reliability calculations to highlight the system reliability difference of various system configurations under harsh conditions.

#### 3.2.2 Realistic MPSoC reliability and our assumption

The reliability function of a single component has been discussed in the previous section. However, for a very complex system with multiple sub-blocks, it is usually difficult to calculate the system reliability by treating it as a flattened entity. A logical approach is to decompose the system into smaller components or functional blocks, compute the reliability function of each sub-block, then derive the system reliability function based on the system structure in which these constituting parts are interconnected.

In a typical MPSoC, processor cores occupy most of the silicon area, hence they can be considered as the main sub-components of the system. As a result of the way they are processed, processor cores on the same die are inherently correlated with each other. In addition, due to the process variations and different load history, each core will have a distinctive reliability distribution. Therefore in a real MPSoC, processor cores are dependent and non-identical components. For mathematical accuracy, the reliability of an MPSoC with non-i.i.d. (independent and identically distributed) components with arbitrary reliability distributions have been studied in [Liu 98] and [Huan 08], etc.

In this thesis, we explore the MPSoC reliability improvement at the system level instead of at the component level. As such, our interest lies in the change of system reliability as a result of various sub-blocks' combination approach such as series, parallel or hybrid. From a system perspective, we are more concerned with the average reliability distribution of the entire MPSoC instead of the exact distribution of each individual core. Moreover, the analysis of system reliability can be mathematically simplified with the assumption that the reliability of each core is independent and identical.

Based on these two reasons, we make the assumption that all the processing cores in a homogeneous MPSoC are the same and have identical and independent reliability distribution (i.i.d.) in our following calculations.

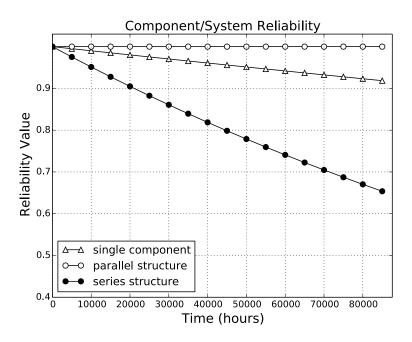

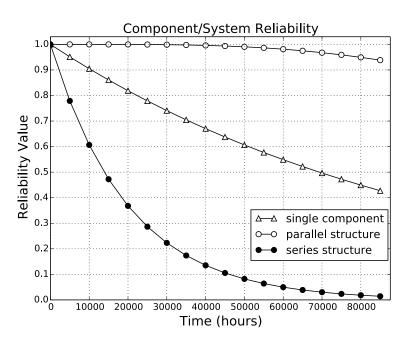

#### 3.2.3 Series and parallel system reliability

A system with series structure describes a system whose correct functional operation depends on the sound operation of every and each constituting block. It

should be noted that the sub-blocks are not necessarily electrically interconnected in a serial fashion, but rather the accomplishment of the system function requires the correct operation of each part. For simplicity, such a system is referred to as a series system in the following context.

Take a system with three sub-blocks as an example. Since all three blocks must be correctly operational in order for the system to be functional, the probability that the system works is the probability that all three blocks work at the same time. Hence, the system reliability in this case is the product of the reliability of each block.

$$R_{sys} = R_1 \times R_2 \times R_3 \tag{3.5}$$

Equation 3.5 can be written in a more generic form. For a series system with N sub-blocks, with the reliability of each block being  $R_1(t)$ ,  $R_2(t)$  till  $R_N(t)$ , the system reliability is:

$$R_{sys}(t) = \prod_{i=1}^{N} R_i(t)$$

(3.6)

In case all the sub-blocks are identical, i.e. all blocks have the same reliability function R(t), the reliability of a series system with N components can be simply calculated as:

$$R_{sys}(t) = R^{N}(t) (3.7)$$

From the equations above, it can be concluded that the reliability of a series system is lower than each of its components. The more blocks are involved in a series system, the lower its overall reliability becomes.

In contrast to the series structure, a system with a parallel structure can have its function accomplished via multiple individual sub-blocks. A system with parallel structure can be described as a system which can correctly perform its specified functions if at least one of its constituting blocks works properly. According to its definition, the parallel system fails only if all of its sub-blocks fail at the same time. As discussed in Section 3.2.1, the failure distribution function can be expressed as: F(t) = 1 - R(t). Hence the reliability of a three-component

parallel system can be expressed as:

$$R_{sys}(t) = 1 - F_{sys}(t) = 1 - F_1(t) \times F_2(t) \times F_3(t)$$

= 1 - [1 - R<sub>1</sub>(t)] \times [1 - R<sub>2</sub>(t)] \times [1 - R<sub>3</sub>(t)] (3.8)

Equation 3.8 can be written in a more generic form. For a parallel system with N sub-blocks, with the reliability of each block being  $R_1(t)$ ,  $R_2(t)$  till  $R_N(t)$ , the system reliability is:

$$R_{sys}(t) = 1 - \prod_{i=1}^{N} [1 - R_i(t)]$$

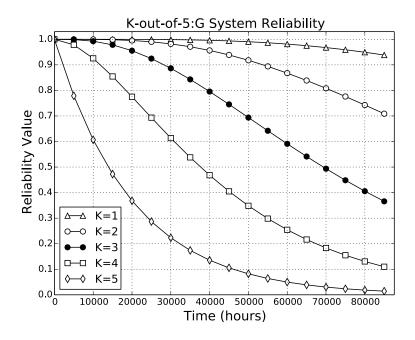

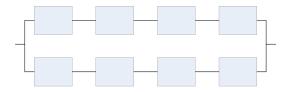

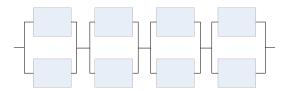

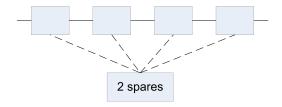

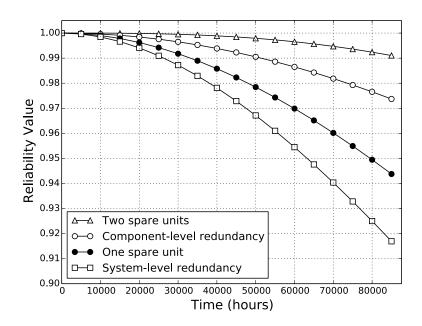

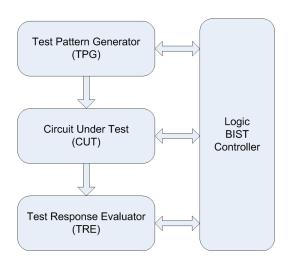

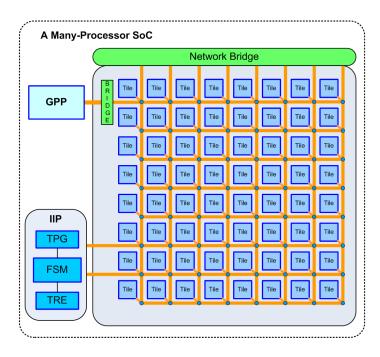

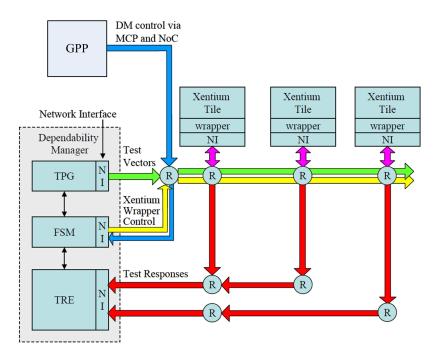

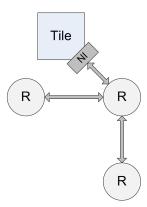

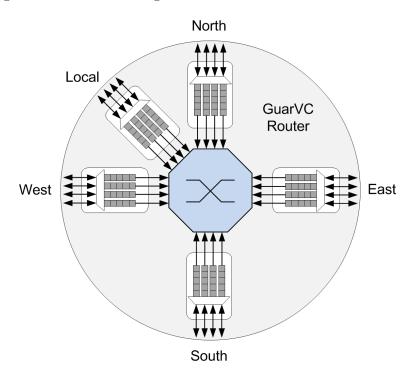

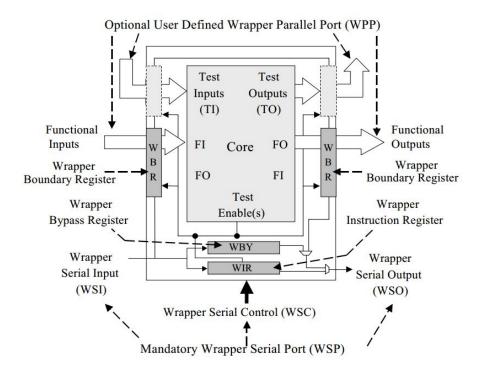

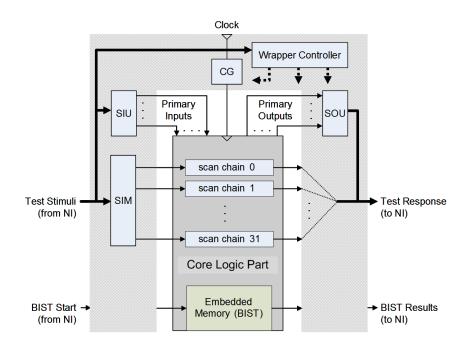

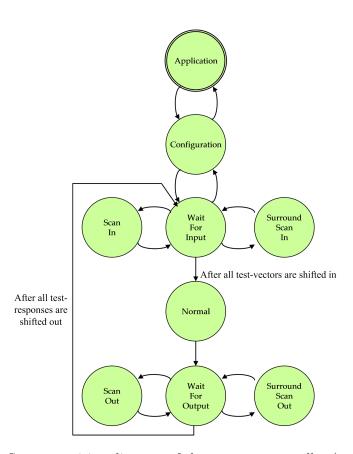

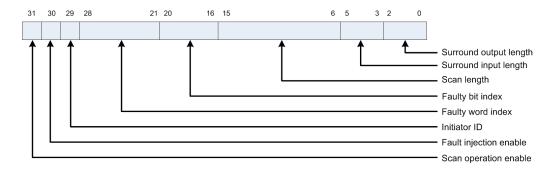

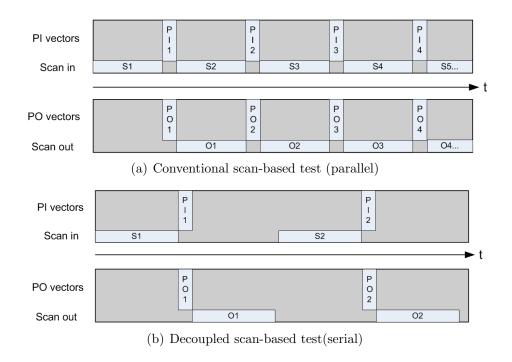

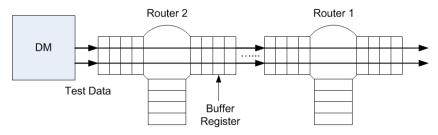

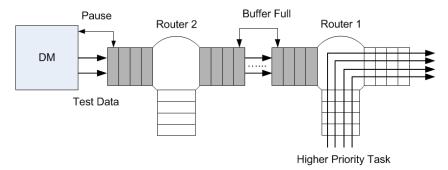

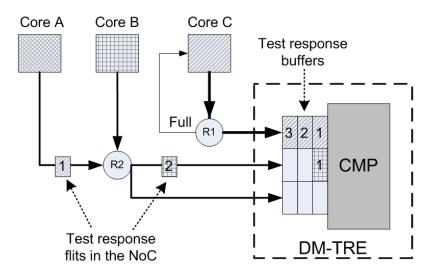

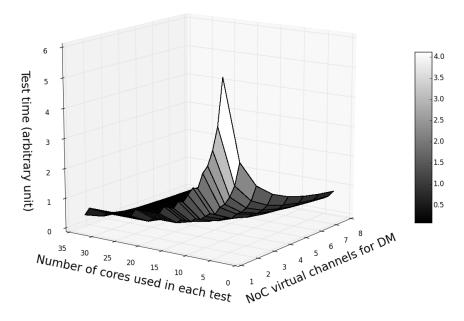

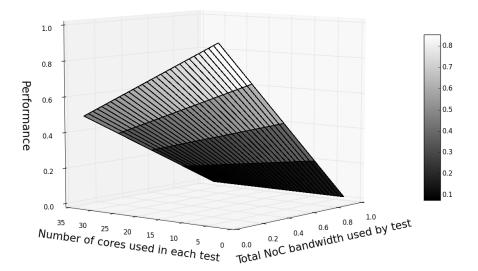

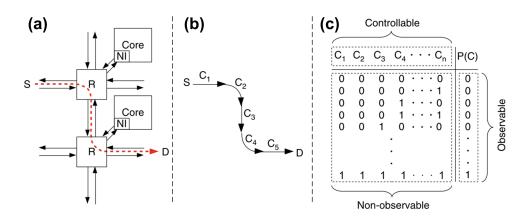

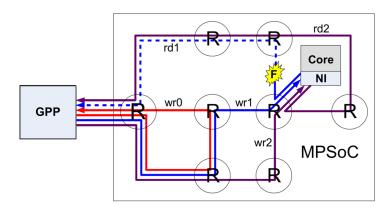

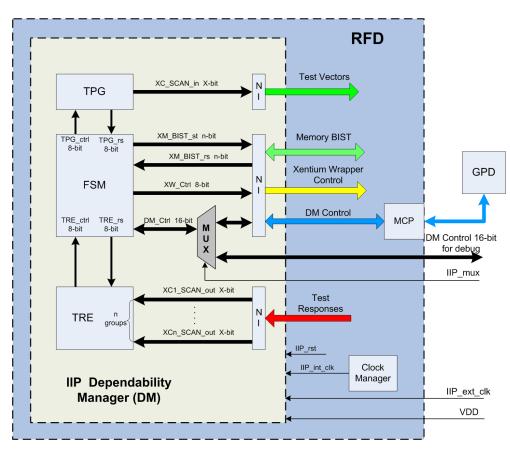

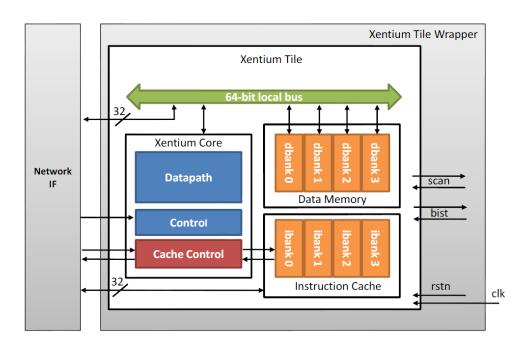

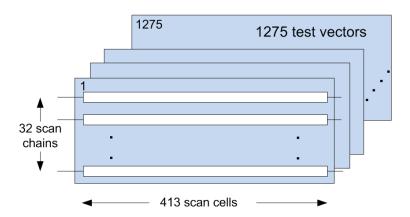

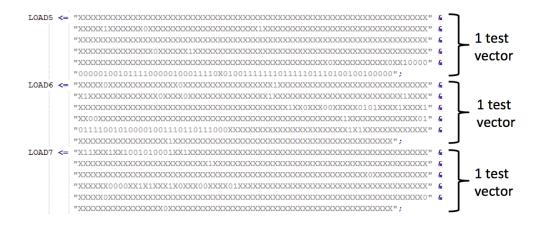

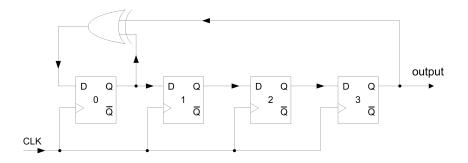

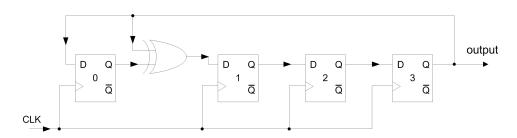

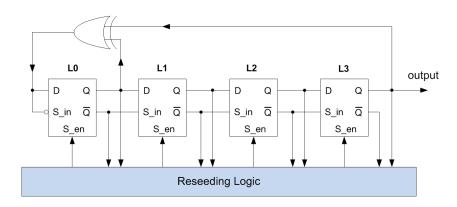

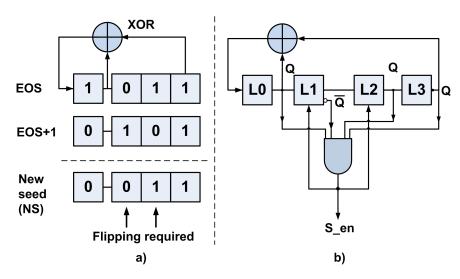

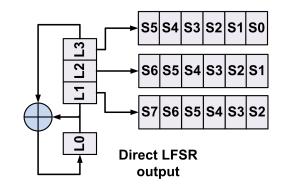

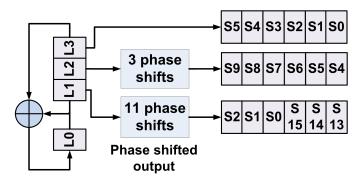

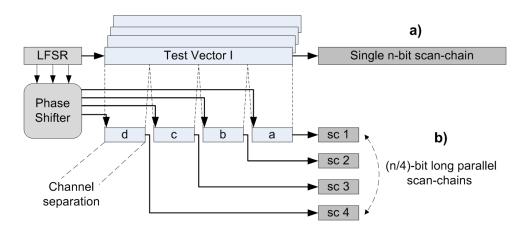

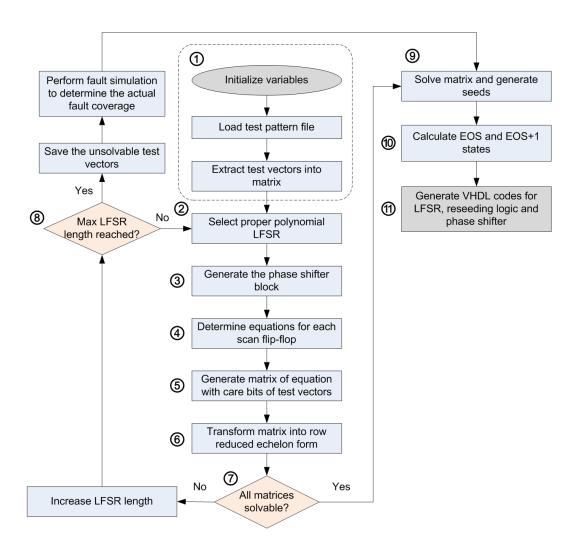

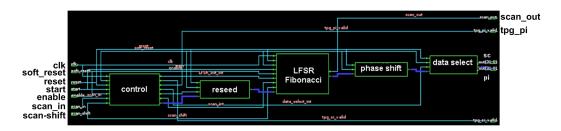

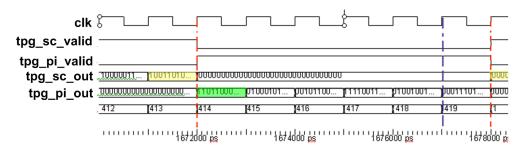

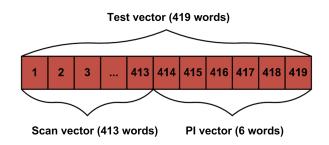

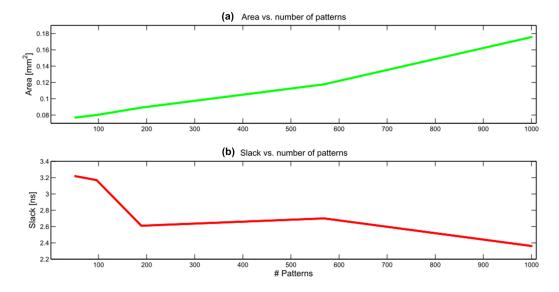

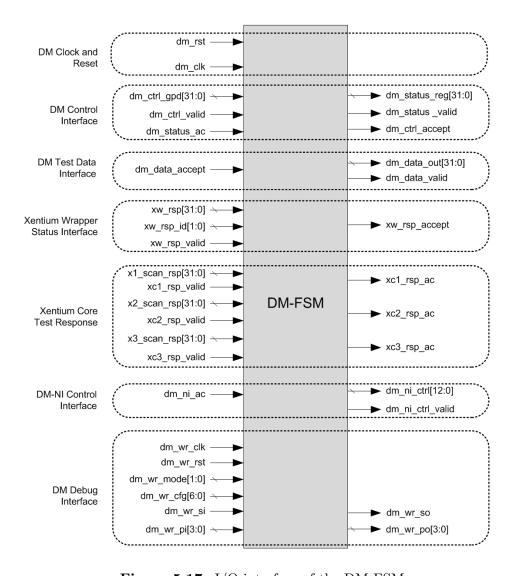

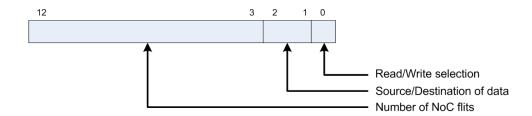

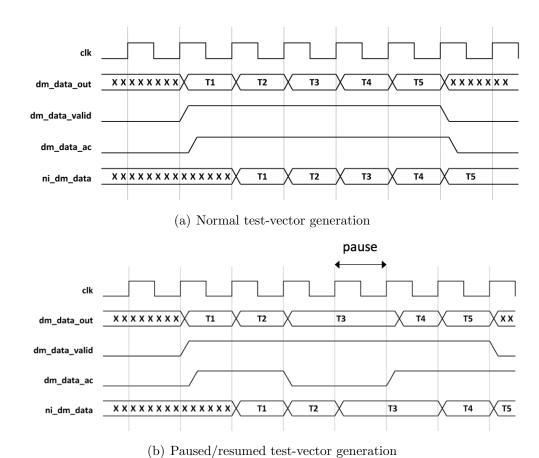

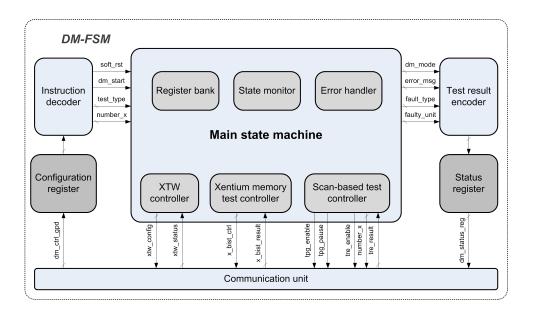

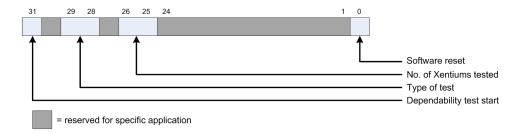

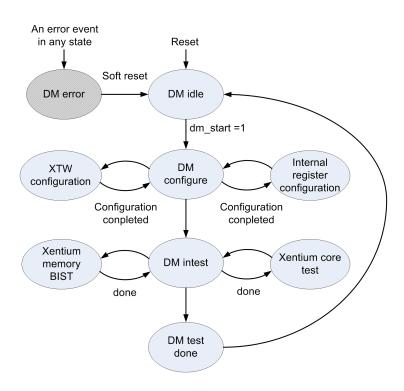

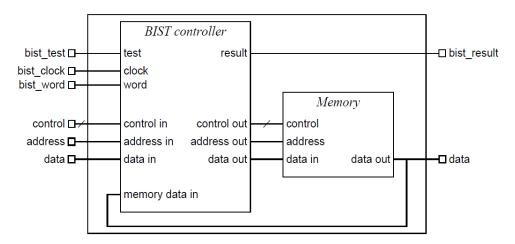

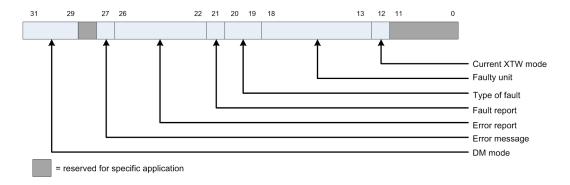

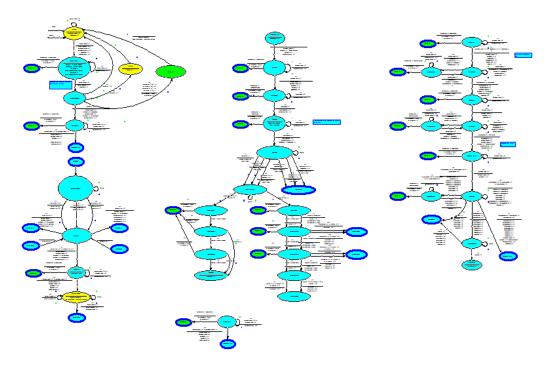

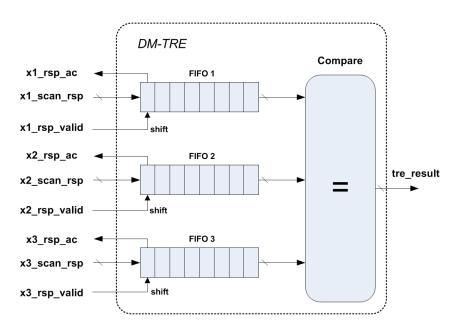

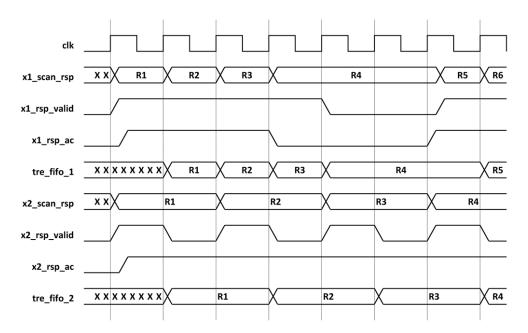

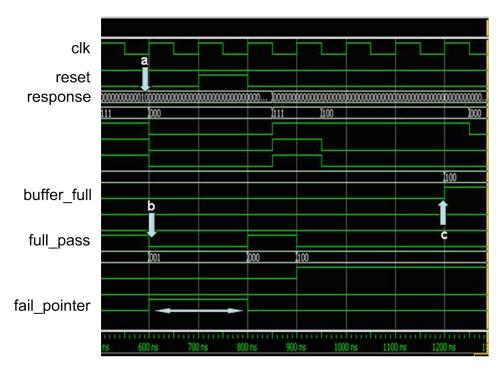

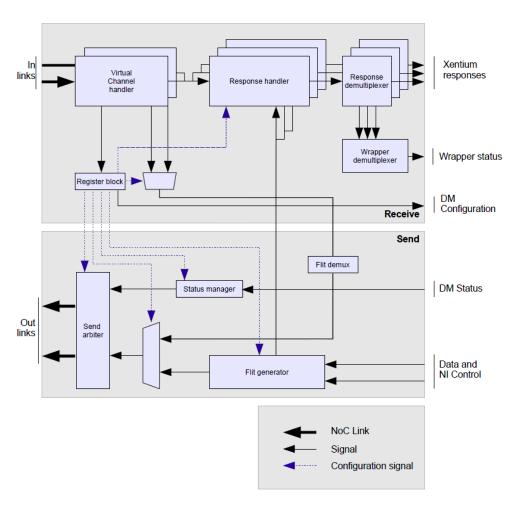

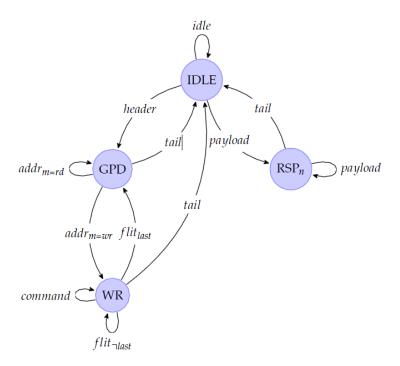

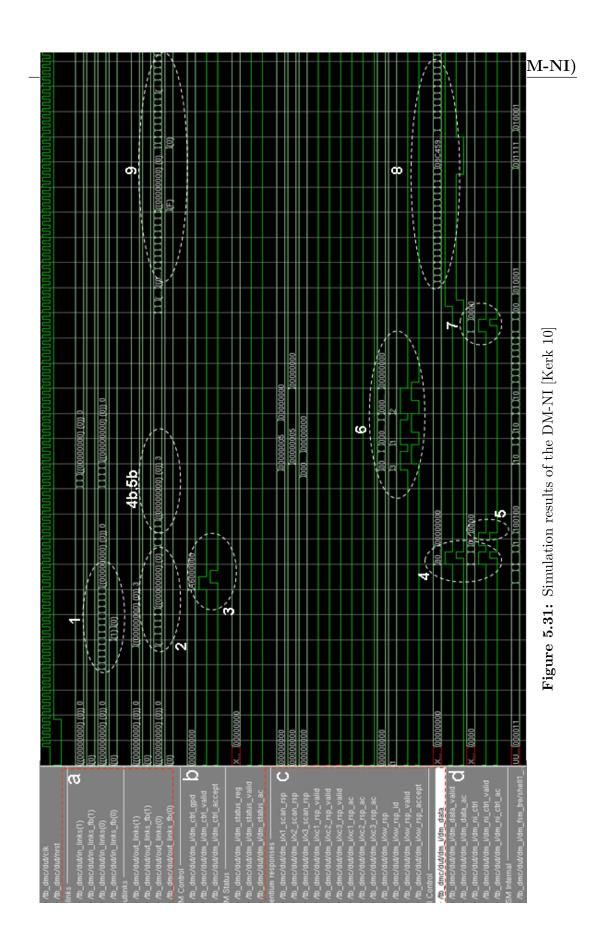

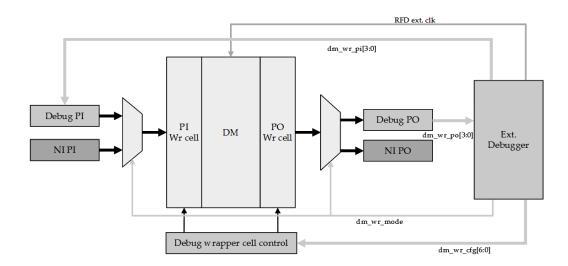

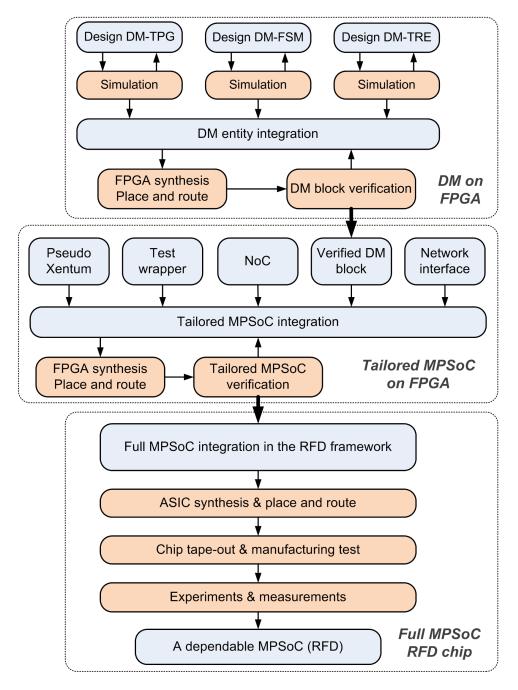

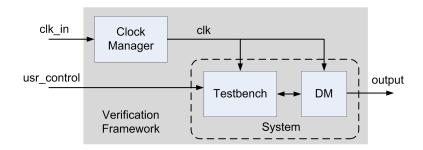

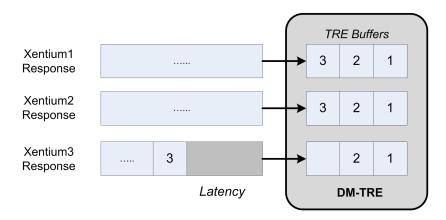

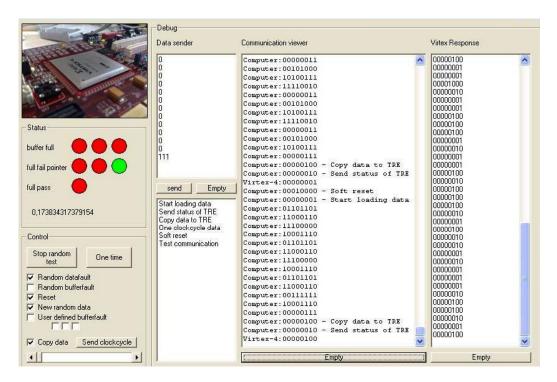

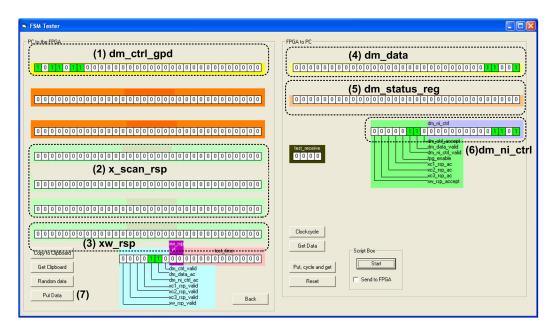

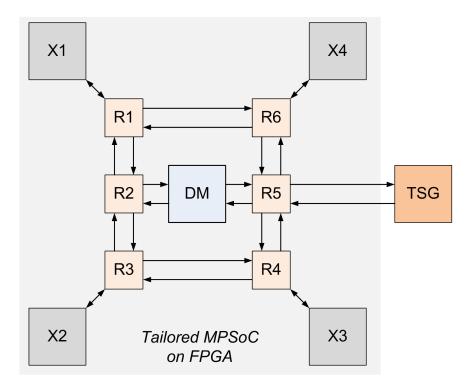

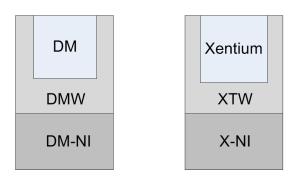

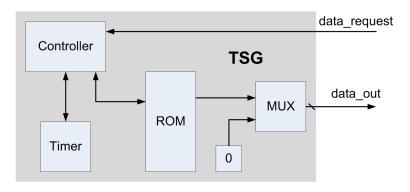

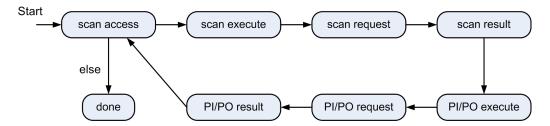

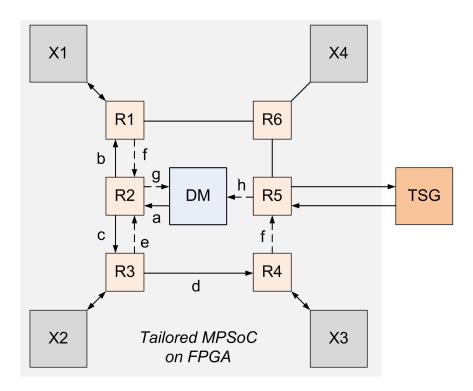

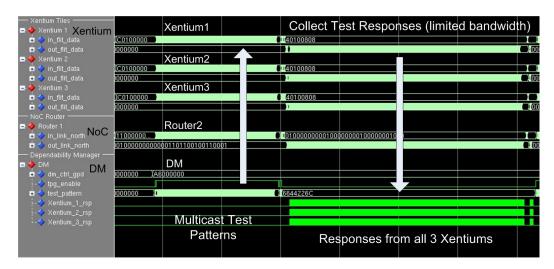

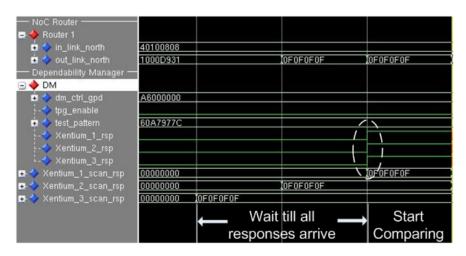

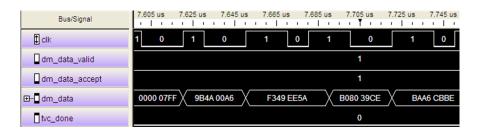

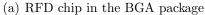

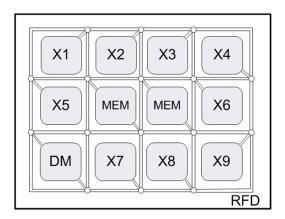

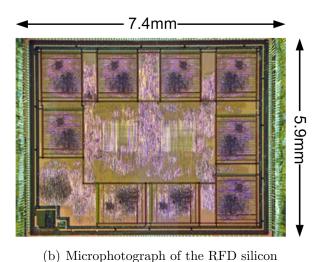

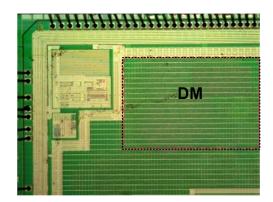

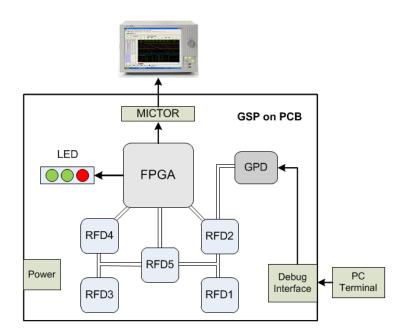

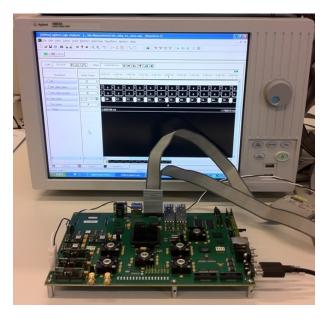

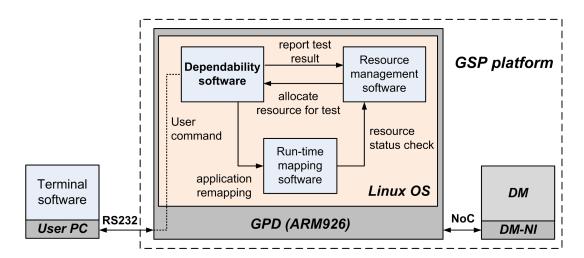

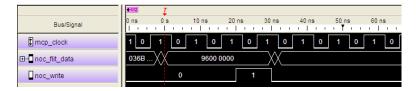

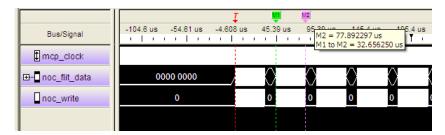

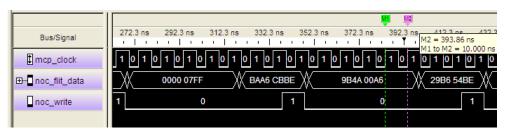

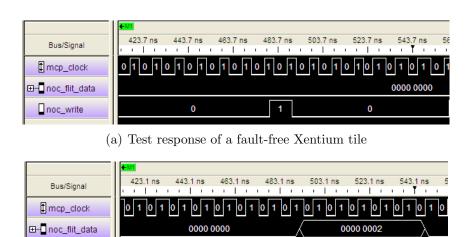

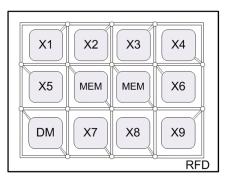

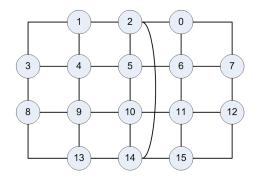

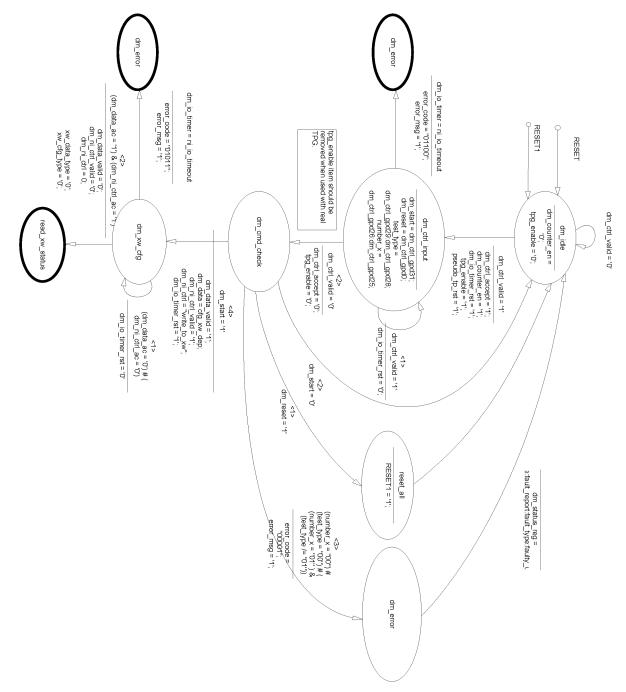

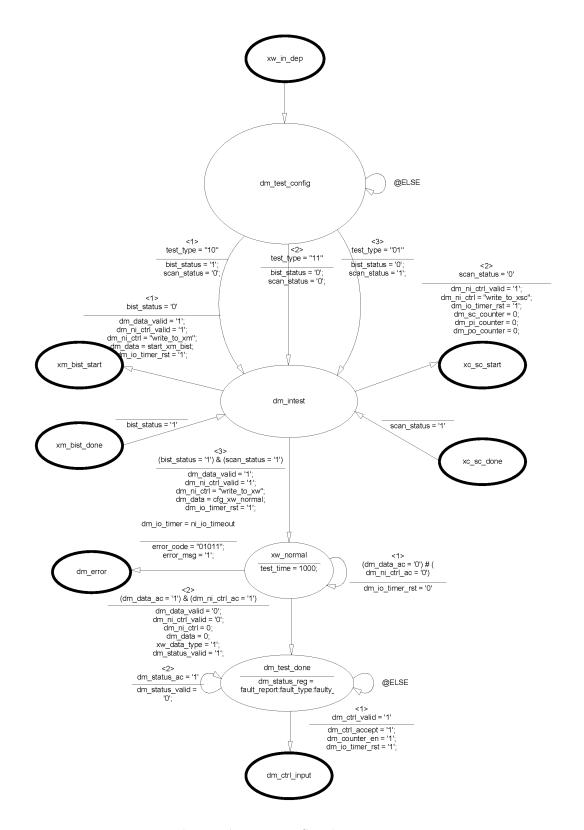

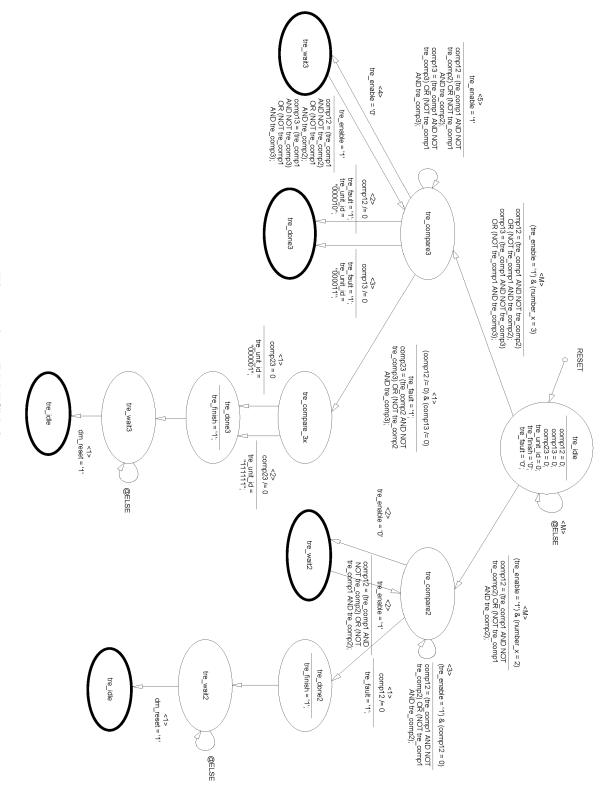

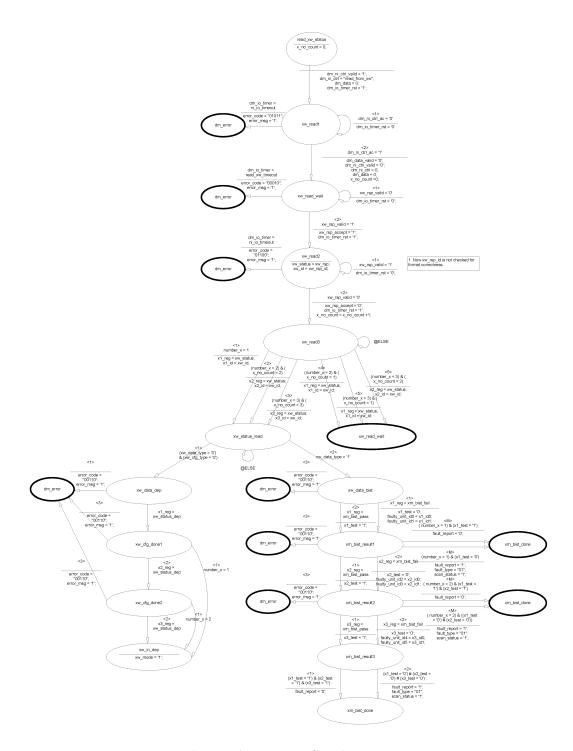

(3.9)